#### **Features**

- 1:10 LVCMOS Output Clock Buffer

- 12kHz to 20MHz additive phase jitter: 25fs(Typical) RMS at 156.25MHz

- Operates DC to 200MHz

- Crystal Input: 8 to 50MHz

- Universal Input: LVPECL,LVDS,HCSL,SSTL, LVCMOS and LVTTL

- Output Skew: 30ps(Typical)

- Total Propagation Delay: 2ns(Typical)

- Synchronous and Glitch-Free Output Enable Is Available

- Spread-spectrum tolerant

- -40 to +85°C,

- 3.3V/2.5V/1.8V/1.5V Core Power Supply

- 3.3V/2.5V/1.8V/1.5V Output Power Supply

- VDDO can't be greater than VDD (VDDO≤ VDD)

- TQFN-32L 5.0 x 5.0mm package

### **Applications**

- Wireless and Wired Infrastructure

- Networking and Data Communications

- Medical electronics

- Portable Test and Measurement

### **Description**

The RS2CB1310 device is a high-performance, low-jitter, low-power clock fanout buffer which can distribute to ten low-jitter LVCMOS clock outputs from one of three inputs, whose primary and secondary inputs can feature differential or single-ended signals and crystal input. Such a buffer is good for use in a variety of mobile and wired infrastructure, data communication, computing, low-power medical imaging, and portable test and measurement applications. When the input is an illegal level, the output is at a defined state. One can set the core to1.5V/1.8V/2.5V or 3.3V, and output to 1.5V/1.8V/2.5V or 3.3V. The overall additive jitter performance is 25fs RMS (typical).

### **Ordering Information**

| Part Number  | Package  | Description    |

|--------------|----------|----------------|

| RS2CB1310ZHE | TQFN-32L | 5.0mm × 5.0 mm |

#### Notes:

[1] E = Pb-free and Green

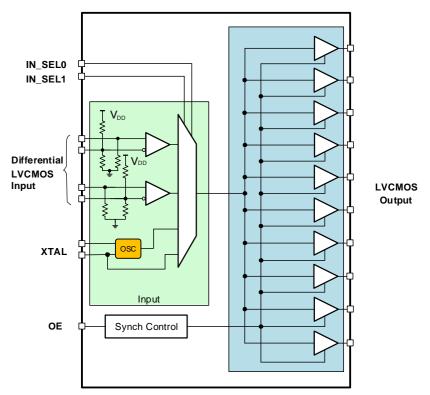

# **Block Diagram**

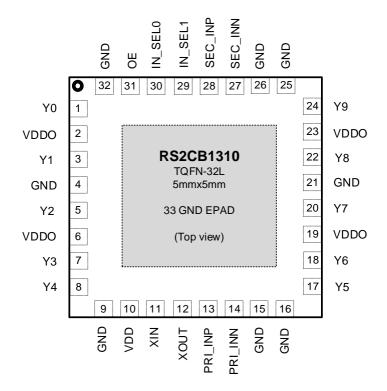

# **Pin Configuration**

Figure 1. Pin Assignments for TQFN-32L Package

2

# **Pin Description**

Table 1. Pin Descriptions

| Pin Name           | Number                                | Туре          | Description                                                                                               | Notes |  |

|--------------------|---------------------------------------|---------------|-----------------------------------------------------------------------------------------------------------|-------|--|

| VDD                | 10                                    | Power         | Power Supply for operating Core and Clock Input.                                                          |       |  |

| VDDO               | 2, 6,19,<br>23                        | Power         | Power Supply for Clock Output.                                                                            |       |  |

| GND                | 4, 9, 15,<br>16, 21,<br>25, 26,<br>32 | GND           | Ground pin.                                                                                               |       |  |

| IN_SEL0<br>IN_SEL1 | 30, 29                                | I, SE, PD     | Clock Input Selection.                                                                                    | 1     |  |

| OE                 | 31                                    | I, SE, PD     | Output Enable. 1 = enable output, 0 = disable output.                                                     | 1     |  |

| XIN                | 11                                    | I, SE         | Crystal input or XTAL bypass mode.                                                                        |       |  |

| XOUT               | 12                                    | O, SE         | Crystal Output. Leave XOUT floating if XIN is driven by a single-ended clock.                             |       |  |

| PRI_INN            | 14                                    | I, DIF        | Primary complementary clock input. Leave PRI_INN floating if PRI_INP is driven by a single-ended clock.   | 2     |  |

| PRI_INP            | 13                                    | I, DIF,<br>SE | Primary true clock input or single-ended clock.                                                           | 3     |  |

| SEC_INN            | 27                                    | O, SE         | Secondary complementary clock input. Leave SEC_INN floating if SEC_INP is driven by a single-ended clock. | 2     |  |

| SEC_INP            | 28                                    | O, SE         | Secondary true clock input or single-ended clock.                                                         | 3     |  |

| Y0                 | 1                                     | O, SE         | LVCMOS Output 0.                                                                                          |       |  |

| Y1                 | 3                                     | O, SE         | LVCMOS Output 1.                                                                                          |       |  |

| Y2                 | 5                                     | O, SE         | LVCMOS Output 2.                                                                                          |       |  |

| Y3                 | 7                                     | O, SE         | LVCMOS Output 3.                                                                                          |       |  |

| Y4                 | 8                                     | O, SE         | LVCMOS Output 4.                                                                                          |       |  |

| Y5                 | 17                                    | O, SE         | LVCMOS Output 5.                                                                                          |       |  |

| Y6                 | 18                                    | O, SE         | LVCMOS Output 6.                                                                                          |       |  |

| Y7                 | 20                                    | O, SE         | LVCMOS Output 7.                                                                                          |       |  |

| Y8                 | 22                                    | O, SE         | LVCMOS Output 8.                                                                                          |       |  |

| Y9                 | 24                                    | O, SE         | LVCMOS Output 9.                                                                                          |       |  |

| EPAD               | 33                                    | GND           | Connect EPAD to ground.                                                                                   |       |  |

<sup>1.</sup> CMOS control input with internal pull-down resistor(150 k $\Omega$ ). 2. Clock input with internal biased to Vdd / 2 (pullup or pulldown of 150 k $\Omega$ ). 3. Clock input with internal pull-down resistor(150 k $\Omega$ ).

### Table 2. Signal Types

| Term  | Description  |

|-------|--------------|

| I     | Input        |

| 0     | Output       |

| PD    | Pull-down    |

| PU    | Pull-up      |

| SE    | Single-ended |

| DIF   | Differential |

| Power | Power        |

| GND   | Ground       |

**Table 3. Input Selection**

| IN_SEL1 | IN_SEL0 | SELECTED INPUT    | Notes |

|---------|---------|-------------------|-------|

| 0       | 0       | PRI_IN            |       |

| 0       | 1       | SEC_IN            |       |

| 1       | 0       | XTAL or overdrive | 1     |

| 1       | 1       | XTAL bypass       | 2     |

<sup>1.</sup> This mode is for XTAL input or overdrive of XTAL oscillator with LVCMOS input. For characteristics; see OUTPUT CHARACTERISTICS. 2. This mode is only XTAL bypass. For characteristics, see OUTPUT CHARACTERISTICS.

#### **Table 4. INPUT/OUTPUT OPERATION**

| INPUT STATE                                     | OUTPUT STATE |

|-------------------------------------------------|--------------|

| PRI_INx, SEC_INx open                           | Logic Low    |

| PRI_INP, SEC_INP = High, PRI_INN, SEC_INN = Low | Logic High   |

| PRI_INP, SEC_INP = Low, PRI_INN, SEC_INN = High | Logic Low    |

<sup>1.</sup> Device must have switching edge to obtain output states.

#### **Table 5. OE Function**

| OE | Yx             |

|----|----------------|

| 0  | High-impedance |

| 1  | Enabled        |

### **Absolute Maximum Ratings**

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the RS2CB1310 at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

**Table 6. Absolute Maximum Ratings**

| Parameter                       | Symbol           | Conditions                              | MIN  | MAX                  | Units | Notes |

|---------------------------------|------------------|-----------------------------------------|------|----------------------|-------|-------|

| Core Supply Voltage             | $V_{DD}$         |                                         | -0.5 | 4.6                  | V     | 1,2   |

| Output Supply Voltage           | $V_{DDO}$        |                                         | -0.5 | 4.6                  | V     | 1,2   |

| Input Voltage                   | V <sub>IN</sub>  |                                         | -0.5 | V <sub>DD</sub> +0.5 | V     |       |

| Output Voltage                  | V <sub>OUT</sub> |                                         | -0.5 | V <sub>DD</sub> +0.5 | ٧     |       |

| Input Current                   | I <sub>IN</sub>  |                                         | -20  | 20                   | mA    |       |

| Output Current                  | I <sub>OUT</sub> |                                         | -50  | 50                   | mA    |       |

| Storage-temperature Temperature | T <sub>STG</sub> |                                         | -65  | 125                  | °C    |       |

| Junction Temperature            | T <sub>J</sub>   | Maximum operating junction temperature. |      | 125                  | °C    |       |

|                                 | 505              | Human Body Model.                       | 2500 |                      | V     |       |

| Input ESD Protection            | ESD              | Charged-device Model                    | 1000 |                      | V     |       |

<sup>1.</sup> The input and output negative voltage ratings may be exceeded if the input and output clamp-current ratings are observed.

## **Recommended Operating Conditions**

**Table 7. Recommended Operating Conditions**

| Parameter                         | Symbol           | Conditions | MIN   | TYP | MAX   | Units | Notes |

|-----------------------------------|------------------|------------|-------|-----|-------|-------|-------|

| 0 0 1 1 1 1                       | \/               |            | 2.375 | 2.5 | 2.625 | .,    |       |

| Core Supply Voltage               | V <sub>DD</sub>  |            | 3.135 | 3.3 | 3.465 | V     |       |

|                                   |                  |            | 1.35  | 1.5 | 1.65  | V 1   |       |

|                                   | V <sub>DDO</sub> |            | 1.6   | 1.8 | 2     |       |       |

| Output Supply Voltage             |                  |            | 2.375 | 2.5 | 2.625 |       | 1     |

|                                   |                  |            | 3.135 | 3.3 | 3.465 |       |       |

| High-level output current, LVCMOS | IOH              |            |       |     | -24   | mA    |       |

| Low-level output current, LVCMOS  | l <sub>OL</sub>  |            |       |     | 24    | mA    |       |

| Operating Temperature             | TA               |            | -40   | 25  | 85    | °C    |       |

5

<sup>2.</sup> This value is limited to 4.6 V maximum.

VDDO can't be greater than VDD (VDDO≤ VDD).

#### **Thermal Information**

#### **Table 8. Thermal Information**

| Package                 | Symbol | Conditions                                   | TYP Value (°C/W) |

|-------------------------|--------|----------------------------------------------|------------------|

|                         | θЈа    | Junction to Ambient                          | 41.5             |

| TOFN/00\ 5.0. 5.0. 0.5  | θJctop | Junction to Case(top)                        | 34.4             |

|                         | θJcbot | Junction to Case(bottom)                     | 6.3              |

| TQFN (32) 5.0×5.0×0.5mm | θЈЬ    | Junction to Board                            | 14.4             |

|                         | Ψυτ    | Junction to Top Characterization Parameter   | 0.9              |

|                         | ψлв    | Junction to Board Characterization Parameter | 14.4             |

### **Current Consumption**

2.375V ≤ VDD ≤ 3.45V, 1.35V ≤ VDDO ≤ VDD, -40°C ≤ TA ≤ 85°C. Typical values represent most likely parametric norms at VDD = VDDO = 3.3V, TA = 25°C, at the Recommended Operation Conditions at the time of product characterization and are not ensured.

**Table 9. Current Consumption**

| Parameter                                | Symbol               | Test Conditions                                                                                                                                                                                                                           | MIN | TYP | MAX | Units | Notes |

|------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|-------|

| Static device Current                    | I <sub>DD</sub>      | $\begin{aligned} \text{OE} &= \text{0V or V}_{\text{DD}}; \\ \text{Ref. input (PRI/SEC)} &= \text{0 V or V}_{\text{DD}}; \\ \text{I}_{\text{O}} &= \text{0mA}; \text{V}_{\text{DD}} / \text{V}_{\text{DDO}} = 3.3 \text{V} \end{aligned}$ |     | 14  |     | mA    | 1     |

|                                          |                      | $OE = 0V \text{ or } V_{DD};$<br>Ref. input (PRI/SEC) = $0V \text{ or } V_{DD};$<br>$I_O = 0mA; V_{DD} / V_{DDO} = 2.5V$                                                                                                                  |     | 8   |     |       |       |

| Device current with<br>XTAL input        | I <sub>DD,XTAL</sub> |                                                                                                                                                                                                                                           |     | 20  |     | mA    | 1     |

|                                          |                      | VDDO=3.465V @100MHz                                                                                                                                                                                                                       |     |     | 8.8 |       |       |

| Power dissipation capacitance per output | $C_PD$               | VDDO=2.625V @100MHz                                                                                                                                                                                                                       |     |     | 7.7 | pF    | 2     |

|                                          |                      | VDDO=2V @100MHz                                                                                                                                                                                                                           |     |     | 7.3 |       |       |

|                                          |                      | VDDO=1.65V @100MHz                                                                                                                                                                                                                        |     |     | 6.9 |       |       |

6

<sup>1.</sup>  $I_{DD}$  and  $I_{DD,XTAL}$  is the current through  $V_{DD}$ ; outputs enabled or in the high-impedance state; no load. 2. This is the formula for the power dissipation calculation (see the *Power Considerations* section)

$I_{DD,Total} = I_{DD} + I_{DD,Cload} + I_{DD,dyn}$  [mA]

$I_{DD, doal} = C_{PD} \times V_{DDO} \times f \times n$  [mA]  $I_{DD, Cload} = C_{load} \times V_{DDO} \times f \times n$  [mA]  $I_{DD, Cload} = C_{load} \times V_{DDO} \times f \times n$  [mA]  $I_{DD, Cload} = C_{load} \times V_{DDO} \times f \times n$  [mA]

### **Input Characteristics**

$2.375V \le VDD \le 3.45V$ ,  $1.35V \le VDDO \le VDD(VDDO \le VDD)$ ,  $-40^{\circ}C \le TA \le 85^{\circ}C$ . Typical values represent most likely parametric norms at VDD = VDDO = 3.3V, TA = 25°C, at the Recommended Operation Conditions at the time of product characterization and are not ensured.

**Table 10. Input Characteristics**

| Parameter                        | Symbol             | Test Conditions                                  | MIN                   | TYP | MAX                   | Units | Notes |

|----------------------------------|--------------------|--------------------------------------------------|-----------------------|-----|-----------------------|-------|-------|

|                                  | DC                 | Characteristic (OE, IN_SEL0, IN_SEL1, PRI_IN     | , SEC_IN)             |     | _                     |       |       |

| Input High Current               | I <sub>IH</sub>    | V <sub>DD</sub> =3.465V, V <sub>IH</sub> =3.465V |                       |     | 40                    |       |       |

| Input Low Current                | I <sub>IL</sub>    | V <sub>DD</sub> =3.465V, V <sub>IH</sub> =0V     |                       |     | -40                   | μA    |       |

| Input edge rate                  | ΔV/ΔΤ              | 20%80%                                           |                       | 2   |                       | V/ns  |       |

| Pullup or pulldown resistance    | R <sub>PU/PD</sub> |                                                  |                       | 150 |                       | kΩ    |       |

| Input capacitance                | C <sub>IN</sub>    |                                                  |                       | 2   |                       | pF    |       |

|                                  |                    | Single-Ended DC Characteristic (PRI_INP, SEC     | C_INP)                |     |                       |       |       |

| loovit High Voltogo              | V                  | V <sub>DD</sub> = 3.3V ±5%                       | 2                     |     | V <sub>DD</sub> +0.3  |       |       |

| Input High Voltage               | V <sub>IH</sub>    | V <sub>DD</sub> = 2.5V ±5%                       | 1.6                   |     | V <sub>DD</sub> +0.3  |       |       |

| Innut Low Voltage                | V <sub>IL</sub>    | $V_{DD} = 3.3V \pm 5\%$                          | -0.3                  |     | 1.3                   |       | 1     |

| Input Low Voltage                | V IL               | V <sub>DD</sub> = 2.5V ±5%                       | -0.3                  |     | 0.9                   |       |       |

|                                  | s                  | ingle-Ended DC Characteristic (OE, IN_SEL0, II   | N_SEL1)               |     |                       |       |       |

| Input High Voltage               | V <sub>IH</sub>    |                                                  | 0.7 x V <sub>DD</sub> |     |                       | V     |       |

| Input Low Voltage                | V <sub>IL</sub>    |                                                  |                       |     | 0.3 x V <sub>DD</sub> | V     |       |

|                                  |                    | Differential DC Characteristic (PRI_IN, SEC_     | _IN)                  |     |                       |       |       |

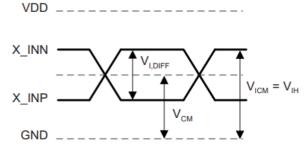

| Differential input voltage swing | VI,DIFF            |                                                  | 0.15                  |     | 1.3                   | .,    | 2     |

| Input common-mode voltage        | VICM               |                                                  | 0.5                   |     | V <sub>DD-0.85</sub>  | V     | 3     |

| _                                |                    | AC Characteristic (PRI_IN, SEC_IN                | _                     |     |                       |       |       |

| Input Frequency                  | F <sub>IN</sub>    |                                                  |                       |     | 200                   | MHz   |       |

| Input duty cycle                 | I <sub>DC</sub>    |                                                  | 40%                   |     | 60%                   |       |       |

<sup>1.</sup> PRI/SEC\_INN biased to VDD/2.

# **Crystal Characteristics**

$2.375V \le VDD \le 3.45V$ ,  $1.35V \le VDDO \le VDD(VDDO \le VDD)$ ,  $-40^{\circ}C \le TA \le 85^{\circ}C$ . Typical values represent most likely parametric norms at VDD = VDDO = 3.3V, TA = 25°C, at the Recommended Operation Conditions at the time of product characterization and are not ensured.

**Table 11. Crystal Characteristics**

| Parameter                          | Test Conditions | MIN | TYP | MAX | Units | Notes |

|------------------------------------|-----------------|-----|-----|-----|-------|-------|

| Equivalent series resistance (ESR) |                 |     | 50  |     | Ω     |       |

| Maximum shunt capacitance          |                 |     | 7   |     | pF    |       |

| Drive level                        |                 |     | 100 |     | μW    |       |

<sup>2.</sup> VIL should not be less than -0.3V.

<sup>3.</sup> Input common-mode voltage is defined as VIH (see Figure 19).

### **Crystal Oscillator Characteristics**

$2.375V \le VDD \le 3.45V$ ,  $1.35V \le VDDO \le VDD(VDDO \le VDD)$ ,  $-40^{\circ}C \le TA \le 85^{\circ}C$ . Typical values represent most likely parametric norms at VDD = VDDO = 3.3V, TA = 25°C, at the Recommended Operation Conditions at the time of product characterization and are not ensured.

**Table 12. Crystal Oscillator Characteristics**

| Parameter                   | Test Conditions | MIN         | TYP | MAX | Units | Notes |

|-----------------------------|-----------------|-------------|-----|-----|-------|-------|

| Mode of oscillation         |                 | Fundamental |     |     |       |       |

| Frequency                   |                 | 8           |     | 50  |       |       |

| Frequency in overdrive mode |                 |             |     | 50  | MHz   | 1     |

| Frequency in bypass mode    |                 |             |     | 50  |       | 2     |

| On-chip load capacitance    |                 |             | 12  |     | pF    |       |

<sup>1.</sup> Input signal swing (max) = 2V; input signal tr (max) = 10ns; tf (max) = 10ns; functional, but device may not meed ac parameters.

### **Output Characteristics**

$2.375V \le VDD \le 3.45V$ ,  $1.35V \le VDDO \le VDD(VDDO \le VDD)$ ,  $-40^{\circ}C \le TA \le 85^{\circ}C$ . Typical values represent most likely parametric norms at VDD = VDDO = 3.3V, TA = 25°C, at the Recommended Operation Conditions at the time of product characterization and are not ensured. Test conditions: load  $50\Omega$  to VDDO/2

**Table 13. Output Characteristics**

| Parameter                     | Symbol              | Test Conditions                                               | MIN      | TYP  | MAX      | Units       | Notes |

|-------------------------------|---------------------|---------------------------------------------------------------|----------|------|----------|-------------|-------|

| Output Skew                   | t <sub>SK(O)</sub>  | Measured between outputs(Ym to Yn)                            |          | 30   | 50       | ps          |       |

| Part-to-Part Skew             | $t_{SK(PP)}$        |                                                               |          |      | 2        | ns          | 1     |

| Propagation Delay Clock IN to | t <sub>DELAY</sub>  | $VDD = 3.3 \text{ V } \pm 5\%, VDDO = 1.35 \text{ V to } VDD$ | 1.5      | 1.95 | 5.0      | ns          |       |

| Clock OUT                     |                     | $VDD = 2.5 \text{ V } \pm 5\%, VDDO = 1.35 \text{ V to } VDD$ | 1.8      | 2.4  | 6.0      |             |       |

|                               |                     | VDDO=3.3V +/- 5%, 20% to 80%                                  | 5.6      | 7.3  | 9.0      | V/ns        |       |

| Output slew rate, rising and  | tslew-rate          | VDDO=2.5V +/- 5%, 20% to 80%                                  | 3.9      | 4.8  | 5.4      |             |       |

| falling                       |                     | VDDO=1.8V +/- 200mV, 20% to 80%                               | 1.6      | 2.1  | 2.5      |             |       |

|                               |                     | VDDO=1.5V +/- 150mV, 20% to 80%                               | 0.9      | 1.2  | 1.4      |             |       |

| Output Frequency              | F <sub>OUT</sub>    |                                                               |          |      | 200      | MHz         |       |

| Output High Voltage           | V <sub>OH</sub>     | VDDO = 3.135V  to  3.465V                                     | 0.8*VDD0 |      |          | -<br>-<br>V |       |

|                               |                     | VDDO = 2.375V to 2.625V                                       | 0.8*VDD0 |      |          |             |       |

|                               |                     | VDDO = 1.6V to 2V                                             | 0.7*VDDO |      |          |             |       |

|                               |                     | VDDO = 1.35V to 1.65V                                         | 0.7*VDDO |      |          |             |       |

| Output Low Voltage            | V <sub>OL</sub>     | VDDO = 3.135V  to  3.465V                                     |          |      | 0.2*VDDO | V           |       |

|                               |                     | VDDO = 2.375V to 2.625V                                       |          |      | 0.2*VDDO |             |       |

|                               |                     | VDDO = 1.6V to 2V                                             |          |      | 0.3*VDDO |             |       |

|                               |                     | VDDO = 1.35V to 1.65V                                         |          |      | 0.3*VDDO |             |       |

|                               | R <sub>CLKOUT</sub> | VDDO = 3.3V                                                   |          | 15   |          | ohm         |       |

|                               |                     | VDDO = 2.5V                                                   |          | 20   |          |             |       |

| Output Resistance             |                     | VDDO = 1.8V                                                   |          | 25   |          |             |       |

|                               |                     | VDDO = 1.5V                                                   |          | 30   |          |             |       |

8

<sup>2.</sup> Input signal swing (max) = VDD; input signal tr (max) = 10ns; ff (max) = 10ns; functional, but device may not meed ac parameters.

|                               |                 | Single-ended input, VDD = 3.3V<br>VDDO = 3.3V                                |     | 25   |     |            |   |

|-------------------------------|-----------------|------------------------------------------------------------------------------|-----|------|-----|------------|---|

| System-level additive jitter  | trjit           | Single-ended input, VDD = 2.5V or 3.3V VDDO = 1.5V,1.8V,2.5V, FIN/OUT=125MHz |     | 30   |     | fs,<br>RMS | 2 |

|                               |                 | Differential input, VDD = 3.3V<br>VDDO = 3.3V                                |     | 30   |     |            |   |

|                               |                 | Differential input, VDD = 2.5V or 3.3V VDDO = 1.5V,1.8V,2.5V, FIN/OUT=125MHz |     | 30   |     |            | 3 |

|                               |                 | 10KHz offset                                                                 |     | -145 |     |            |   |

|                               | NF              | 100KHz offset                                                                |     | -156 |     |            |   |

|                               |                 | 1MHz offset                                                                  |     | -163 |     |            |   |

| Noise floor                   |                 | 10MHz offset                                                                 |     | -164 |     |            |   |

|                               |                 | 20MHz offset                                                                 |     | -164 |     | dBc/Hz     |   |

|                               |                 | 10KHz offset                                                                 |     | -145 |     |            |   |

|                               |                 | 100KHz offset                                                                |     | -155 |     |            |   |

|                               |                 | 1MHz offset                                                                  |     | -160 |     |            | 4 |

|                               |                 | 10MHz offset                                                                 |     | -161 |     |            | • |

|                               |                 | 2-MHz offset                                                                 |     | -162 |     |            |   |

| Output duty cycle             | O <sub>DC</sub> | FIN/OUT=125MHz, I <sub>DC</sub> = 50%                                        | 45% |      | 55% |            | 5 |

| Output enable or disable time | ten             |                                                                              |     |      | 2   | Cycle      |   |

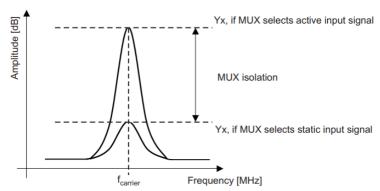

| MUX isolation                 | MUXISOLATION    | 125MHz                                                                       | 55  |      |     | dB         | 6 |

- 1. Calculation for part-to-part skew is the difference between the fastest and the slowest tpd across multiple devices.

- 2. Integration range: 12KHz-20MHz; input source see the System-Level Additive-Jitter Measurement section.

- 3. Single-ended input,  $f_{IN/OUT} = 125MHz$ , VDD = VDDO = 3.3V.

- 4. Differential input,  $f_{IN/OUT} = 125MHz$ , VDD = VDDO = 3.3V.

- 5. Stable  $V_{IH}$ ,  $V_{IL}$ , and  $V_{CM}$

- 6. See Figure 18.

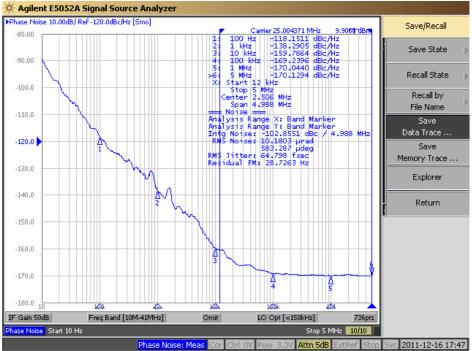

### PHASE NOISE WITH XTAL SELECTED

VDD = VDDO = 2.5V or 3.3V,  $f_{XTAL} = 25MHz$ ,  $TA = 25^{\circ}C$  (unless otherwise noted). The selected XTAL specification refer to NOTE 1.

#### **Table 14. PHASE NOISE**

| Parameter        | Symbol | Test Conditions                                                                | MIN | TYP  | MAX | Units  | Notes |

|------------------|--------|--------------------------------------------------------------------------------|-----|------|-----|--------|-------|

| DMO 1 ""         |        | IB = 12kHz to $5MHz$ , $VDD = VDDO = 3.3V$                                     |     | 80   |     |        |       |

| RMS phase jitter | Jrms   | IB = 12kHz to 5MHz, VDD = VDDO = 2.5V                                          |     | 115  |     | fs rms |       |

|                  |        | $f_{offset} = 100Hz, VDD = VDDO = 3.3V$                                        |     | -92  |     | dBc/Hz | 1     |

|                  | PN     | $f_{offset} = 1kHz, VDD = VDDO = 3.3V$                                         |     | -137 |     |        |       |

|                  |        | f <sub>offset</sub> = 10kHz, VDD = VDDO = 3.3V                                 |     | -163 |     |        |       |

|                  |        | $f_{offset} = 100kHz, VDD = VDDO = 3.3V$                                       |     | -168 |     |        |       |

|                  |        | $f_{offset} = 1MHz, VDD = VDDO = 3.3V$                                         |     | -168 |     |        |       |

| Phase noise (see |        | $f_{offset} = 5MHz, VDD = VDDO = 3.3V$                                         |     | -169 |     |        |       |

| Figure 15)       |        | f <sub>offset</sub> = 100Hz, VDD = VDDO = 2.5V                                 |     | -91  |     |        |       |

|                  |        | $f_{offset} = 1kHz, VDD = VDDO = 2.5V$                                         |     | -136 |     |        |       |

|                  |        | f <sub>offset</sub> = 10kHz, VDD = VDDO = 2.5V                                 |     | -159 |     |        |       |

|                  |        | $f_{\text{offset}} = 100 \text{kHz}, \text{ VDD} = \text{VDDO} = 2.5 \text{V}$ |     | -164 |     |        |       |

|                  |        | f <sub>offset</sub> = 1MHz, VDD = VDDO = 2.5V                                  |     | -165 |     |        |       |

|                  |        | $f_{\text{offset}} = 5\text{MHz}, \text{VDD} = \text{VDDO} = 2.5\text{V}$      |     | -165 |     |        |       |

9

<sup>1.</sup> Crystal specification: CL = 18pF; ESR = 35Ω (max); C0 = 7pF; drive level = 100μW (max).

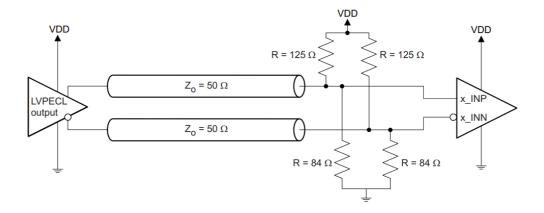

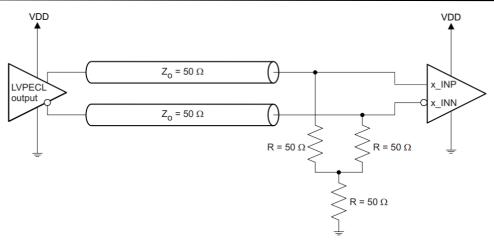

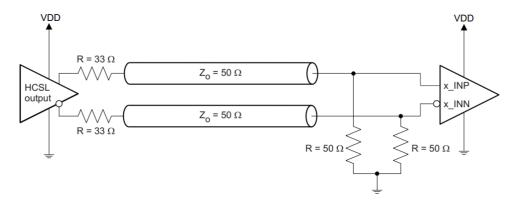

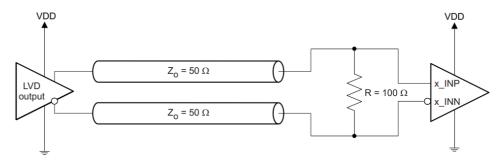

#### **TEST CONFIGURATIONS**

Figure 2 through Figure 8 illustrate how to set up the device for a variety of test configurations.

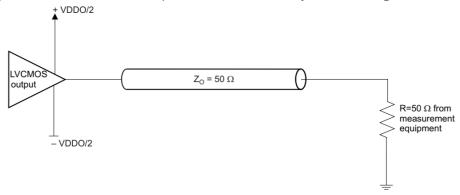

Figure 2. LVCMOS Output DC Configuration; Test Load Circuit

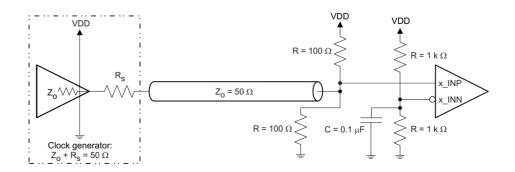

Figure 3. LVCMOS Input DC Configuration During Device Test

Figure 4. LVPECL Input Configuration During Device Test

Figure 5. LVPECL Input Configuration During Device Test

Figure 6. HCSL Input Configuration During Device Test

Figure 7. LVDS Input Configuration During Device Test

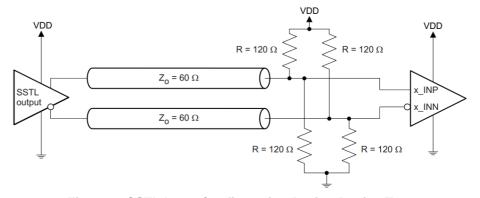

Figure 8. SSTL Input Configuration During Device Test

11

#### **APPLICATION INFORMATION**

### **Typical Application Load**

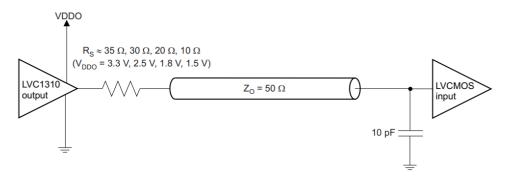

Figure 9. LVCMOS Output DC Configuration: Typical Application Load

### **Parameter Measurement Information**

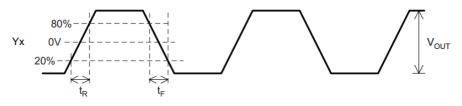

Figure 10. LVCMOS Output Voltage, and Rise and Fall Times

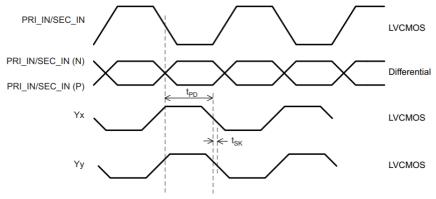

Figure 11. Differential and Single-Ended Output Skew and Propagation Delay

### **Crystal Oscillator Input**

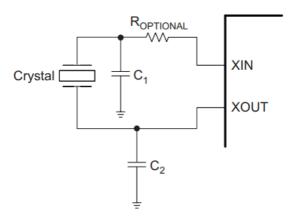

The crystal oscillator circuit is characterized with 18-pF parallel-resonant crystals. Choices of C1 and C2 were to minimize the ppm error. Optional resistor  $R_{\mathsf{OPTIONAL}}$  limits the drive level of the oscillator circuit.

Figure 12. Crystal Reference Input

The input XIN can accept single-ended LVCMOS signals in two configurations. It is possible to overdrive the oscillator stage or to use a pure LVCMOS input (see Table 3). If overdriving the oscillator stage, it is necessary to ac-couple the input with a capacitor (see Figure 13). Otherwise, if selecting the bypass, there is no requirement for a coupling capacitor.

#### **NOTE**

1. If using the overdrive or bypass mode, the device is functional, but may not meet its ac parameters.

Figure 13. Single-Ended Crystal Input

#### **Phase-Noise Performance**

The RS2CB1310 provides ultralow phase-noise outputs (noise floor = -170dBc/Hz) if it has an attached crystal. Figure 14 shows the phase-noise plot of the RS2CB1310 with a 25-MHz crystal at  $V_{DD} = V_{DDO} = 3.3V$  and room temperature.

Figure 14. Phase-Noise Profile With 25-MHz Crystal at Nominal Conditions

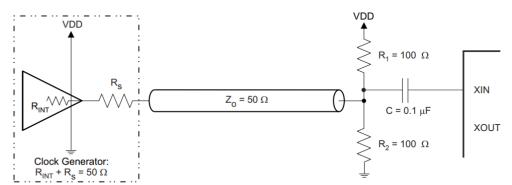

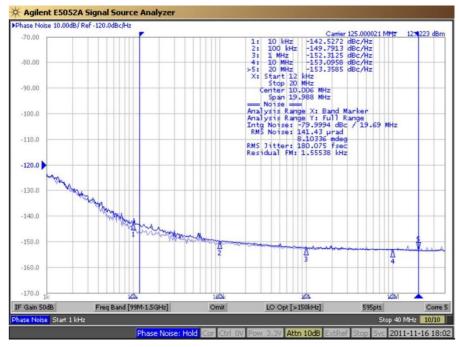

### System-Level Additive-Jitter Measurement

For high-performance devices, limitations of the equipment influence phase-noise measurements. The noise floor of the equipment often exceeds the noise floor of the device. The real noise floor of the device is probably lower (see Output Characteristics). Phase noise is influenced by the input source and the measurement equipment.

Figure 15. Input Phase Noise (179.4 fs, Light Blue) and Output Phase Noise (180 fs, Dark Blue)

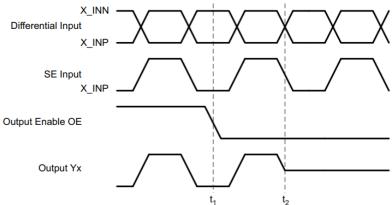

### **Output Enable**

Pulling OE to LOW  $(t_1)$ , forces the outputs to the high-impedance state after the next falling edge of the input signal  $(t_2)$ . The outputs remain in the high-impedance state as long as OE is LOW (see Figure 16).

Figure 16. OE: Disable Outputs

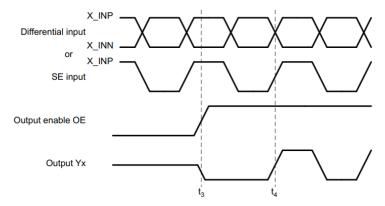

If the outputs are in the high-impedance state, pulling OE to HIGH forces all outputs LOW asynchronously  $(t_3)$ . Within two clock cycles (maximum), the outputs start switching again  $(t_4)$ , after a falling edge of the input signal (see Figure 17).

Figure 17. OE: Enable Outputs

If the outputs are in the high-impedance state and the input is static (no clock signal), OE works fully asynchronously. A transition of OE from LOW to HIGH forces the outputs to LOW. A transition from HIGH to LOW does not force to the high-impedance state again. Therefore, a state change requires a falling edge of the input signal (see Figure 16).

#### **MUX** Isolation

The definition of MUX isolation is the difference in output amplitude (dB) between an active and a static input signal.

Figure 18. Output Spectrum of an Active and a Static Input Signal

# **Differential Input Level**

NOTE: The calculation for VCM is:  $V_{CM} = V_{DD} - V_{ICM} - V_{I,DIFF}/2$

Figure 19. Differential Input Level

#### **Power Considerations**

The following power consideration refers to the device-consumed power consumption only. The device power consumption is the sum of static power and dynamic power. The dynamic power usage consists of two components:

- Power used by the device as it switches states

- Power required to charge any output load

The output load can be capacitive-only or capacitive and resistive. Use the following formula to calculate the power consumption of the device:

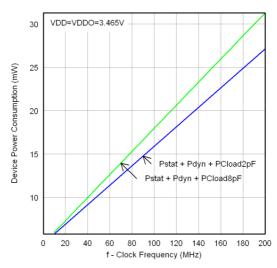

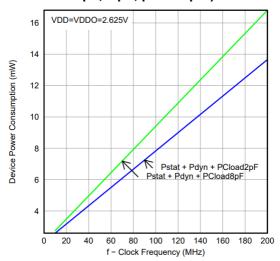

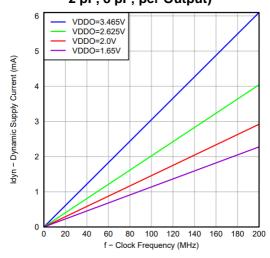

```

\begin{split} P_{Dev} &= P_{stat} + P_{dyn} + P_{Cload} \, (\text{see Figure 20 and Figure 21}) \\ P_{stat} &= I_{DD} \times V_{DD} \\ P_{dyn} + P_{Cload} &= (I_{DD,dyn} + I_{DD,Cload}) \times V_{DDO} \\ \text{where:} \\ I_{DD,dyn} &= C_{PD} \times V_{DDO} \times f \times n \, [\text{mA}] \, (\text{see Figure 22}) \\ I_{DD,Cload} &= C_{load} \times V_{DDO} \times f \times n \, [\text{mA}] \end{split}

```

Example for power consumption of the RS2CB1310: 10 outputs are switching, f = 100MHz,  $V_{DD} = V_{DDO} = 3.3V$  and assuming  $C_{load} = 2pF$  per output:

```

\begin{split} P_{Dev} &= 46.2 \text{mW} + 117.5 \text{mW} = 163.7 \text{mW} \\ P_{stat} &= 14 \text{ mA} \times 3.3 \text{V} = 46.2 \text{mW} \\ P_{dyn} + P_{Cload} &= (29 \text{mA} + 6.6 \text{ mA}) \times 3.3 \text{V} = 117.5 \text{mW} \\ I_{DD,dyn} &= 8.8 \text{pF} \times 3.3 \text{V} \times 100 \text{MHz} \times 10 = 29 \text{mA} \\ I_{DD,Cload} &= 2 \text{pF} \times 3.3 \text{V} \times 100 \text{MHz} \times 10 = 6.6 \text{mA} \end{split}

```

#### **NOTE**

1. For dimensioning the power supply, consider the total power consumption. The total power consumption is the sum of device power consumption and the power consumption of the load.

16

Figure 20. Device Power Consumption versus Clock Frequency (VDD = VDDO = 3.465 V; Load 2 pF, 8 pF; per Output)

Figure 21. Device Power Consumption versus Clock Frequency (VDD = VDDO = 2.625 V; Load 2 pF, 8 pF; per Output)

Figure 22. Dynamic Supply Current versus Clock Frequency (per Output)

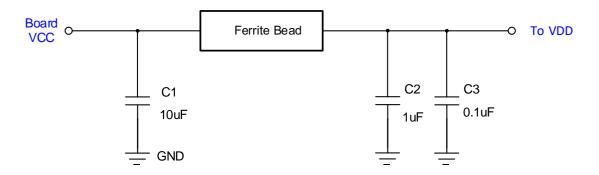

### **Power Supply Filtering**

It is recommended, but not required, to insert a ferrite bead between the board power supply and the chip power supply to isolate the high-frequency switching noises generated by the clock driver, preventing them from leaking into the board supply. Choosing an appropriate ferrite bead with very low DC resistance is important, because it is imperative to provide adequate isolation between the board supply and the chip supply. It is also imperative to maintain a voltage at the supply terminals that is greater than the minimum voltage required for proper operation.

High-performance clock buffers are sensitive to noise on the power supply, which can dramatically increase the additive jitter of the buffer. Thus, it is essential to reduce noise from the system power supply, especially when jitter or phase noise is very critical to applications.

Use of filter capacitors eliminates the low-frequency noise from power supply, where the bypass capacitors provide the very low-impedance path for high-frequency noise and guard the power-supply system against induced fluctuations. The bypass capacitors also provide instantaneous current surges as required by the device, and should have low ESR. To use the bypass capacitors properly, place them very close to the power supply pins and lay out traces with short loops to minimize inductance. RSM recommends to adding as many high-frequency (for example, 0.1-µF) bypass capacitors as there are supply pins in the package.

Figure 23. Power-Supply Decoupling

Raystar Microelectronics Technology Inc.

# **Package Information**

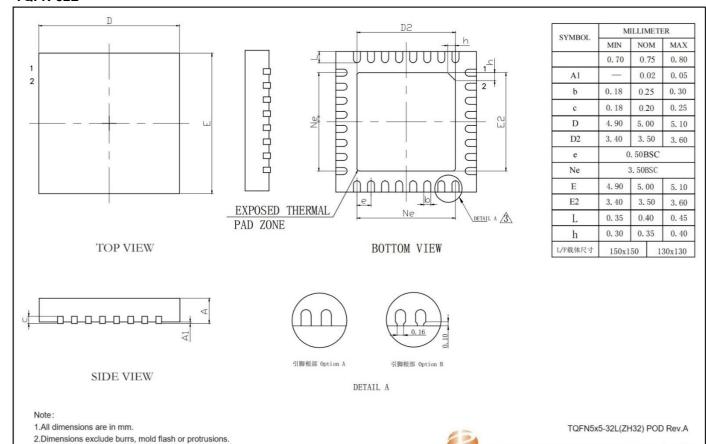

#### TQFN-32L

3.Refer Jedec MO-220

# **Revision History**

| Revision | Description         | Date       |

|----------|---------------------|------------|

| 0.9      | Preliminary release | 2024/06/21 |

| 1.0      | 1. Initial release  | 2025/7/8   |