#### **Features**

Operating Frequency: 0MHz~200 MHz

Low noise: <50fs rms</li>low skew: < 50ps</li>

• Fast rise/fall time: 1.0ns typ.

• Propagation delay: 2.5ns typ.

• Industrial temperature (-40°C to 125°C)

• 3.3V/2.5V/1.8V power supply

AEC-Q100 qualified, Automotive Grade 1 support; PPAP capable, and manufactured in IATF 16949 certified facilities

• Packaging (Pb-free & Green available)

## **Applications**

- 33 MHz PCI-to-133 MHz PCIX controllers

- 80 MHz for 10/100 Mbps Ethernet

- 125 MHz for Gigabit networking

- 155.520 MHz for Optical OC3/SDH/SONET

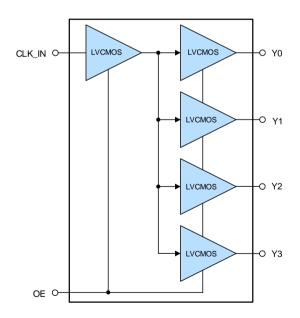

## **Block Diagram**

Figure 1 Block Diagram

## **Description**

Raystar's RS304 are low-skew, low- noise, high speed clock buffers and are ideal for computing, networking, and communication applications. Application examples include PCI(X) clock buffers in servers and workstations, PCI(X) Storage Area Network (SAN), and RAID controllers. They are used for networking and communications applications requiring 80 MHz for 10/100 Mbps Ethernet and 125 MHz for Gigabit networking clocks. To reduce EMI emission and power consumption, all outputs can be disabled to Low-state by asserting a low signal to the OE (Output Enable) pin. RS304 output impedance is 50 ohms.

#### **Order Information**

| Part Number | Package    | Description  |

|-------------|------------|--------------|

| RS304QWE    | 8-Pin SOIC | 4.9mmx6mm    |

| RS304QUE    | 8-Pin MSOP | 3.2mmx5.15mm |

| RS304QZAE   | 8-Pin DFN8 | 2mmx2mm      |

#### Notes

1

[1] E = Pb-free and Green

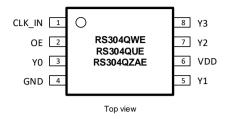

# **Pin Configuration**

Table 1 Function table

| INPUT  |    | OUTPUT |

|--------|----|--------|

| CLK_IN | OE | Y[0:3] |

| Х      | L  | L      |

| L      | Н  | L      |

| Н      | Н  | Н      |

## **Pin Description**

| Pin name | Pin No. | Туре   | Description                                                                |

|----------|---------|--------|----------------------------------------------------------------------------|

| CLK_IN   | 1       | Input  | Clock input                                                                |

| OE       | 2       | Input  | Active High Output Enable. Y[0:3] outputs will be Low Level when OE is low |

| Y[0:3]   | 3,5,7,8 | Output | LVCMOS level outputs                                                       |

| GND      | 4       | Ground | Ground                                                                     |

| VDD      | 6       | Power  | 3.3V/2.5V/1.8V Power Supply                                                |

2 RSM-DS-R-0176

## **Absolute Maximum Ratings**

| Parameter                                         | Range             |

|---------------------------------------------------|-------------------|

| Supply Voltage (VDD)                              | -0.0V to +6.5V    |

| Input Voltage                                     | -0.5V to VDD+0.5V |

| Operating Temperature                             | -40°C to +125°C   |

| Storage Temperature                               | -65°C to +150°C   |

| Junction Temperature                              | 150°C             |

| Input ESD MIL- 883, method 3015, human body model | 2KV               |

## **Recommended Operating Conditions**

| Symbol | Parameter                      | MIN  | MAX  | Unit |

|--------|--------------------------------|------|------|------|

| VDD    | I/O Supply, Analog Core Supply | 1.71 | 3.63 | V    |

| TA     | Ambient Temperature            | -40  | 125  | ° C  |

## **DC Electrical Characteristics**

$(TA = -40 \sim 125^{\circ}C, VCC = 3.3V \pm 10\%, 2.5V \pm 10\%, 1.8V \pm 5\%)$

| Symbol          | Parameter           | Conditions                | MIN     | TYP | MAX      | Unit |

|-----------------|---------------------|---------------------------|---------|-----|----------|------|

| VıL             | Low Input Voltage   |                           |         |     | 0.8      | V    |

| VIH             | High Input Voltage  |                           | 0.6*VDD |     |          | V    |

| I <sub>IL</sub> | Low Input Current   | VIN = 0V                  |         |     | -5       |      |

| Іін             | High Input Current  | VIN = VDD                 |         |     | 5        | μA   |

| Vol             | Low Output Voltage  | I <sub>OL</sub> = 12mA    |         |     | 0.25*VDD |      |

| Vон             | High Output Voltage | I <sub>OH</sub> = - 12mA  | 0.7*VDD |     |          | V    |

| Co              | Output Capacitance  |                           |         | 3   | 7        | n.E  |

| Cı              | Input Capacitance   |                           |         | 3   | 5        | pF   |

|                 |                     | CL = 15pF/100MHz VDD=3.3V |         | 32  |          |      |

| I <sub>DD</sub> | Supply Current      | CL = 15pF/100MHz VDD=2.5V |         | 26  |          | mA   |

|                 |                     | CL = 15pF/100MHz VDD=1.8V |         | 20  |          |      |

| Zo              | Output Impedance    |                           |         | 50  |          | Ω    |

| L               | Pin Inductance      |                           |         |     | 7        | nH   |

## **AC Characteristics**

$(TA = -40 \sim 125$ °C, VCC = 3.3V  $\pm 10\%$ , 2.5V  $\pm 10\%$ , 1.8V  $\pm 5\%$ , 15pF/100MHz)

| Symbol                | Parameter                     | Conditions                             | MIN | TYP | MAX | Unit |

|-----------------------|-------------------------------|----------------------------------------|-----|-----|-----|------|

| F <sub>IN</sub>       | Input frequency               |                                        | 0   |     | 200 | MHz  |

|                       |                               | CLK_IN to Y[0-3] rising edges @ 1.5V   | 1.0 | 1.7 | 3.0 |      |

| T <sub>PLH</sub>      | Low-to-high propagation delay | CLK_IN to Y[0-3] rising edges @ 1.25V  | 1.0 | 2.0 | 3.2 |      |

|                       |                               | CLK_IN to Y[0-3] rising edges @ 0.9V   | 1.0 | 2.5 | 3.5 |      |

|                       |                               | CLK_IN to Y[0-3] falling edges @ 1.5V  | 1.0 | 1.7 | 3.0 | ns   |

| T <sub>PHL</sub>      | High-to-low propagation delay | CLK_IN to Y[0-3] falling edges @ 1.25V | 1.0 | 2.0 | 3.2 |      |

|                       |                               | CLK_IN to Y[0-3] falling edges @ 0.9V  | 1.0 | 2.5 | 3.5 |      |

| T <sub>SK(O)</sub>    | Output skew                   | @ VDD/2                                |     |     | 100 |      |

| T <sub>SK(P)</sub>    | Pulse skew                    | @ VDD/2                                |     |     | 300 | 20   |

| T <sub>SK(T)</sub>    | Package skew(1)               | @ VDD/2                                |     |     | 500 | ps   |

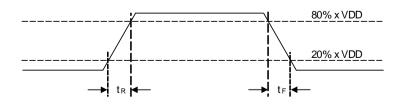

|                       |                               | 20%~80% VDD=3.3V                       |     | 0.7 | 1.4 |      |

| $T_R, T_F$            | Rise, Fall time               | 20%~80% VDD=2.5V                       |     | 1   | 2   |      |

|                       |                               | 20%~80% VDD=1.8V                       |     | 1.5 | 3   | ns   |

| $T_{PZL}, T_{PZH}$    | Output enable time            |                                        |     |     | 5   |      |

| $T_{PLZ}$ , $T_{PHZ}$ | Output disable time           |                                        |     |     | 10  |      |

| T <sub>DC</sub>       | Output duty cycle             | tDC = tH/tC Y, tH = High Pulse Width   | 45  |     | 55  | %    |

#### Note:

- 1. Identical traces, loads, power supply.

- 2. Maximum Output Skew is 100ps when frequency is below 125MHz with 10pF loading.

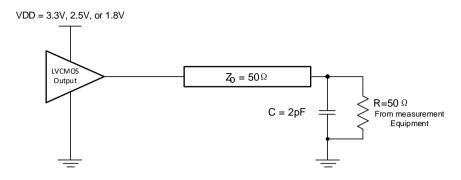

## **Parameter Measurement Information**

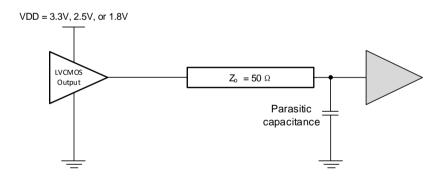

**Test Load Circuit**

Application Load With 50-Ω Termination

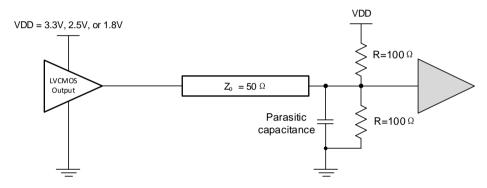

**Application Load With Termination**

**Rise and Fall Time**

5 RSM-DS-R-0176

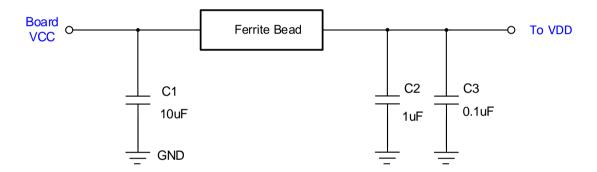

### **Power Supply Recommendations**

High-performance clock buffers can be sensitive to noise on the power supply, which may dramatically increase the additive jitter of the buffer. Thus, it is essential to manage any excessive noise from the system power supply, especially for applications where the jitter and phase noise performance is critical.

Filter capacitors are used to eliminate the low-frequency noise from the power supply, where the bypass capacitors provide the very low impedance path for high-frequency noise and guard the power supply system against induced fluctuations. These bypass capacitors also provide instantaneous current surges as required by the device and should have low equivalent series resistance (ESR). To properly bypass the supply, the decoupling capacitors must be placed very close to the power-supply terminals, be connected directly to the ground plane, and laid out with short loops to minimize inductance. TI recommends adding as many high-frequency (for example, 0.1 µF) bypass capacitors, as there are supply terminals in the package. TI recommends, but does not require, inserting a ferrite bead between the board power supply and the chip power supply that isolates the high-frequency switching noises generated by the clock buffer; these beads prevent the switching noise from leaking into the board supply. It is imperative to choose an appropriate ferrite bead with very low DC resistance to provide adequate isolation between the board supply and the chip supply, as well as to maintain a voltage at the supply terminals that is greater than the minimum voltage required for proper operation.

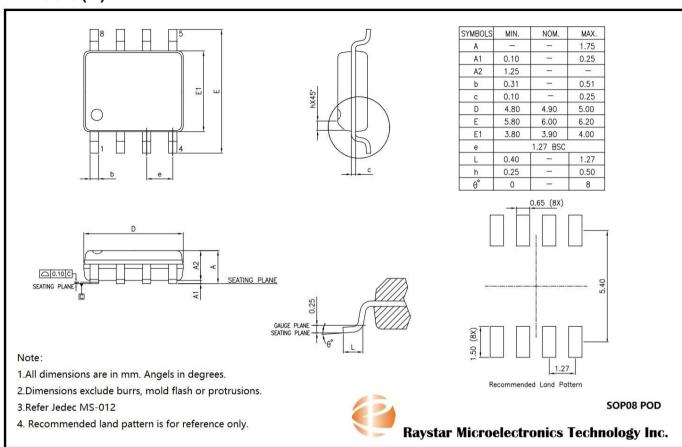

## **Package Information**

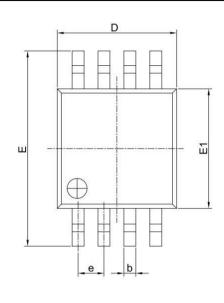

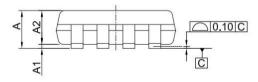

## 8-Pin SOIC (W)

## 8-Pin MSOP (U)

| PKG D  | IMENSION | S(MM) |

|--------|----------|-------|

| SYMBOL | Min.     | Max.  |

| А      |          | 1.10  |

| A1     | 0.00     | 0.15  |

| A2     | 0.75     | 0.95  |

| b      | 0.22     | 0.38  |

| С      | 0.08     | 0.23  |

| D      | 2.80     | 3.20  |

| Е      | 4.65     | 5.15  |

| E1     | 2.80     | 3.20  |

| е      | 0.65     | BSC   |

| L      | 0.40     | 0.80  |

| L1     | 0.95     | REF   |

| θ      | 0°       | 8°    |

#### Note:

- 1.All dimensions are in mm. Angels in degrees.

- 2.Refer Jedec MO-187

- 3. Dimensions exclude burrs, mold flash or protrusions.

MSOP08 POD Rev.0

**Raystar Microelectronics Technology Inc.**

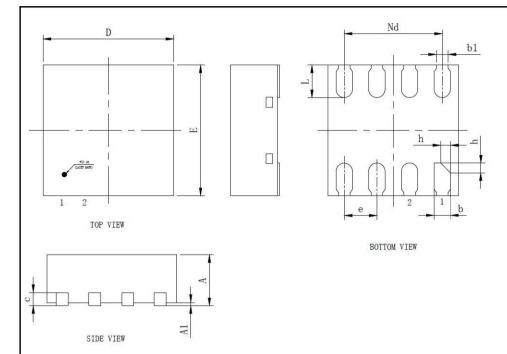

## 8-Pin DFN8 (ZA)

| esza (Dot | MILLIMETER |          |       |

|-----------|------------|----------|-------|

| SYMBOL    | MIN        | NOM      | MAX   |

| A         | 0.70       | 0.75     | 0.80  |

| A1        | 0          | 0.02     | 0. 05 |

| b         | 0. 18      | 0.25     | 0. 30 |

| b1        |            | 0.18REF  |       |

| c         | 0.203REF   |          |       |

| D         | 1. 90      | 2. 00    | 2. 10 |

| e         |            | 0. 50BSC | 1     |

| Nd        |            | 1.50BSC  |       |

| E         | 1. 90      | 2.00     | 2. 10 |

| L         | 0. 45      | 0.50     | 0. 55 |

| h         | 0. 10      | 0.15     | 0. 20 |

#### Notes:

- 1. All dimensions are in mm. Angles in degrees.

- 2. Refer JEDEC MO-229

- 3. Dimensions exclude burrs, mold flash or protrusions.

DFN 2X2X0.75-8L(ZA08) POD Rev.0

Raystar Microelectronics Technology Inc.

9 RSM-DS-R-0176

## **Revision History**

| Revision | Description     | Date       |

|----------|-----------------|------------|

| V0.9     | Preliminary     | 2025/05/28 |

| V1.0     | Initial release | 2025/07/16 |