#### **Features**

- 2-bit bidirectional translator for SDA and SCL lines in mixed-mode I<sup>2</sup>C-bus applications

- Standard-mode, Fast-mode, and Fast-mode Plus I<sup>2</sup>C-bus and SMBus compatible

- Less than 1.5 ns propagation delay

- Allows voltage level translation between:

1.0 V VREF1 and 1.8 V $\sim$ 5 V VREF2

1.2 V VREF1 and 1.8 V $\sim$ 5 V VREF2

1.5 V VREF1 and 2.5 V  $\sim$  5 V VREF2

1.8 V VREF1 and 3.3 V $\sim$ 5 V VREF2

2.5 V VREF1 and 3.3 V $\sim$ 5 V VREF2

3.3 V VREF1 and 5 V VREF2

- Bidirectional voltage translation with no direction pin

- Low 3.5 ohm ON-state connection between input and output ports provides less signal distortion

- 5 V tolerant I<sup>2</sup>C-bus I/O ports to support mixed-mode signal operation

- Lock-up free operation for isolation when EN = LOW

- Flow through pin out for ease of printedcircuit board trace routing

- ESD protection exceeds 4000V HBM

- Extended Temperature: -40°C to +85°C

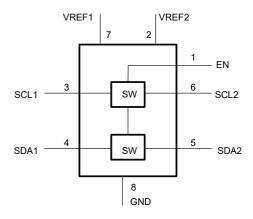

### **Block Diagram**

Figure 1: Block Diagram

#### **Description**

The RS7LS9306 is a dual bidirectional  $I^2C$ -bus and SMBus voltage-level translator with an enable (EN) input, and is operational from 1.0 V to 3.3 V ( $V_{REF1}$ ) and 1.8 V to 5.5 V( $V_{REF2}$ ).

The RS7LS9306 allows bidirectional voltage translations between 1.0 V and 5 V without the use of a direction pin. The low ON-state resistance (Ron) of the switch allows connections to be made with minimal propagation delay. When EN is HIGH, the translator switch is on, and the SCL1 and SDA1 I/O are connected to the SCL2 and SDA2 I/O respectively, allowing bidirectional data flow between ports. When EN is LOW, the translator switch is off, and a high- impedance state exists between ports.

The RS7LS9306 is not a bus buffer that provides both level translation and physically isolates to either side of the bus when both sides are connected. The RS7LS9306 only isolates both sides when the device is disabled and provides voltage level translation when active.

The translator provides excellent ESD protection to lower voltage devices, and at the same time protects less ESD-resistant devices.

#### **Ordering Information**

| Part Number  | Package | Description       |

|--------------|---------|-------------------|

| RS7LS9306ZEE | DFN-8   | 8-pin, 2.0x3.0 mm |

| RS7LS9306TE  | SOT23-8 | 8-Pin, SOT23      |

| RS7LS9306VE  | VSSOP8  | 2.0mmx2.3mm       |

#### Notes:

1. E = Pb-free and Green

# **Pin Configuration**

| ;       | SOT23-8(Top view    | )       | DFN-8   | 3 (Top vie        | ew)  |       |       | V | SSOP8(Top view)    |   |       |

|---------|---------------------|---------|---------|-------------------|------|-------|-------|---|--------------------|---|-------|

| GND 1   |                     | 8 EN    | GND 1   |                   | 8 E  | ΞN    | GND   | 1 |                    | 8 | EN    |

| VREF1 2 | RS7LS9306           | 7 VREF2 | VREF1 2 | RS7LS9306         | 7 V  | /REF2 | VREF1 | 2 | RS7LS9306          | 7 | VREF2 |

| SCL1 3  | SOT23-8<br>Top View | 6 SCL2  | SCL1 3  | DFN-8<br>Top View | 6 S0 | CL2   | SCL1  | 3 | VSSOP8<br>Top View | 6 | SCL2  |

| SDA1 4  |                     | 5 SDA2  | SDA1 4  |                   | 5 S  | SDA2  | SDA1  | 4 |                    | 5 | SDA2  |

| Pin<br>Name       | Pin NO.<br>SOT23 | Pin NO.<br>DFN-8 | Pin NO.<br>VSSOP8 | Description                                                                    |

|-------------------|------------------|------------------|-------------------|--------------------------------------------------------------------------------|

| GND               | 1                | 1                | 1                 | Ground                                                                         |

| V <sub>REF1</sub> | 2                | 2                | 2                 | Low-voltage-side reference supply voltage for SCL1 and SDA1                    |

| SCL1              | 3                | 3                | 3                 | Serial clock, low-voltage side. Connect to VREF1 through a pullup resistor.    |

| SDA1              | 4                | 4                | 4                 | Serial data, low-voltage side. Connect to VREF1 through a pullup resistor.     |

| SDA2              | 5                | 5                | 5                 | Serial data, high-voltage side. Connect to VREF2 through a pullup resistor.    |

| SCL2              | 6                | 6                | 6                 | Serial clock, high-voltage side. Connect to VREF2 through a pullup resistor.   |

| V <sub>REF2</sub> | 7                | 7                | 7                 | High-voltage-side reference supply voltage for SCL2 and SDA2                   |

| EN                | 8                | 8                | 8                 | Switch enable input. Connected to VREF2 and pulled up through a high resistor. |

# **Absolute Maximum Ratings**

| Symbol             | Parameter                                  |      | TYP | MAX  | Unit |

|--------------------|--------------------------------------------|------|-----|------|------|

| T <sub>store</sub> | Storage Temperature                        | -65  | -   | +150 | °C   |

| Vcca               | DC Supply Voltage port B                   | -0.3 | -   | 6.0  | V    |

| Vccb               | DC Supply Voltage port A                   | -0.3 | -   | 6.0  | V    |

| $V_{IOB}$          | Vi(A) referenced DC Input / Output Voltage | -0.3 | -   | 6.0  | V    |

| V <sub>IOB</sub>   | Vi(B) referenced DC Input / Output Voltage | -0.3 | -   | 6.0  | V    |

| $V_{EN}$           | Enable Control Pin DC Input Voltage        | -0.3 | -   | 6.0  | V    |

| Існ                | Channel Current                            |      |     | 128  | mA   |

#### Notes:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Recommended operation conditions**

| Symbol              | Parameter                      |     | TYP | MAX | Unit |

|---------------------|--------------------------------|-----|-----|-----|------|

| $V_{I/O}$           | Voltage on an input/output pin | 0   | -   | 5.5 | V    |

| $V_{REF1}$          | Reference voltage1             | 0   | -   | 5.5 | V    |

| V <sub>REF2</sub>   | Reference bias voltage 2       | 0   | -   | 5.5 | V    |

| V <sub>I(EN)</sub>  | Input voltage on pin EN        | 0   | -   | 5.5 | V    |

| I <sub>(pass)</sub> | Pass switch current            | -   | •   | 64  | ns/V |

| T <sub>A</sub>      | Ambient temperature            | -40 | •   | 85  | °C   |

## **DC Electrical Characteristics**

$T_A = -40 \, ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ; unless otherwise specified

| Parameter   | Description                            | Test Conditions (1            | MIN            | <b>TYP</b> (2) | MAX  | Unit |    |

|-------------|----------------------------------------|-------------------------------|----------------|----------------|------|------|----|

| Input and o | utput SDAB and SCLB                    |                               |                |                |      |      |    |

| Vıĸ         | input clamping voltage                 | II = -18mA; VI(EN) = (        | ) V            | -              | -    | -1.2 | V  |

| Įıн         | HIGH-level input current               | VI = 5 V; VI(EN) = 0 \        | /              | -              | -    | 5    | μΑ |

| Ci(EN)      | input capacitance on pin EN            | VI = 3 V or 0 V               |                | -              | 11   | -    | pF |

|             | Off-state input/output                 | Vo = 3 V or 0 V; VI(EN) = 0 V |                |                |      |      |    |

| Cio(off)    | capacitance (SCLn,<br>SDAn)            |                               |                | -              | 4    | -    | pF |

|             | on-state input/output                  |                               |                |                |      |      |    |

| Cio(on)     | capacitance(SCLn,<br>SDAn)             | Vo = 3 V or 0 V; V(i          | EN) = 3 V      | -              | 10.5 | ı    | pF |

|             |                                        |                               | VI(EN) = 4.5 V | -              | 3.5  | 5.5  | Ω  |

|             |                                        | VI = 0V;                      | VI(EN) = 3 V   | -              | 4.7  | 7    | Ω  |

| Ron         | ON-state resistance(2)<br>(SCLn, SDAn) | I○=64mA                       | VI(EN) = 2.3 V | -              | 6.3  | 9.5  | Ω  |

| 1.011       |                                        |                               | VI(EN) = 1.5 V | -              | 15   | 60   | Ω  |

|             |                                        | V= 2.4V;<br>lo=15mA           | VI(EN) = 4.5 V | 1              | 6    | 15   | Ω  |

#### Notes:

- 1. All typical values are at  $T_A = 25$  °C.

- Measured by the voltage drop between the SCL1 and SCL2, or SDA1 and SDA2 terminals at the indicated current through the switch. ON-state resistance is determined by the lowest voltage of the two terminals.

# **AC** characteristics

$T_A$  = -40 °C to +85 °C; unless otherwise specified. Values guaranteed by design.

|                   |                                                                  |                                                                                        | C <sub>L</sub> = | 50 pF | C <sub>L</sub> = 3 | 30 pF | C <sub>L</sub> = | 15 pF |      |

|-------------------|------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------|-------|--------------------|-------|------------------|-------|------|

| Symbol            | Parameter                                                        | Conditions                                                                             | MIN              | MAX   | MIN                | MAX   | MIN              | MAX   | Unit |

|                   | ic characteristics (                                             |                                                                                        |                  |       |                    |       |                  |       |      |

| $V_{I(EN)} = 3$ . | $.3 \text{ V}; \text{ V}_{\text{IH}} = 3.3 \text{ V}; \text{ V}$ | $I_{IL} = 0 \text{ V}; \text{ V}_{M} = 1.15 \text{ V}$                                 |                  |       |                    |       |                  |       |      |

| t <sub>PLH</sub>  | LOW-to-<br>HIGH<br>propagation<br>delay                          | from (input) SCL2 or SDA2 to (output) SCL1 or SDA1                                     | 0                | 0.8   | 0                  | 0.6   | 0                | 0.3   | ns   |

| t <sub>PHL</sub>  | HIGH-to-<br>LOW<br>propagation<br>delay                          | from (input) SCL2 or SDA2 to<br>(output) SCL1 or SDA1                                  | 0                | 1.2   | 0                  | 1     | 0                | 0.5   | ns   |

| $V_{I(EN)} = 2$ . | .5 V; V <sub>IH</sub> = 2.5 V; V                                 | $V_{1L} = 0 \text{ V}; \text{ V}_{M} = 0.75 \text{ V}$                                 | II.              | 1     |                    | I.    |                  | l l   |      |

| t <sub>PLH</sub>  | LOW-to-<br>HIGH<br>propagation<br>delay                          | from (input) SCL2 or SDA2 to<br>(output) SCL1 or SDA1                                  | 0                | 1     | 0                  | 0.7   | 0                | 0.4   | ns   |

| t <sub>PHL</sub>  | HIGH-to-<br>LOW<br>propagation<br>delay                          | from (input) SCL2 or SDA2 to<br>(output) SCL1 or SDA1                                  | 0                | 1.3   | 0                  | 1     | 0                | 0.6   | ns   |

|                   | ic characteristics (                                             |                                                                                        | •                |       |                    | •     |                  |       |      |

| $V_{I(EN)} = 3$ . | $.3 \text{ V; V}_{IH} = 2.3 \text{ V; V}_{IH}$                   | $V_{1L} = 0 \text{ V}; \text{ V}_{T} = 3.3 \text{ V}; \text{ V}_{M} = 1.15 \text{ V};$ |                  |       |                    |       |                  |       |      |

| t <sub>PLH</sub>  | LOW-to-<br>HIGH<br>propagation<br>delay                          | ffrom (input) SCL1 orSDA1 to (output) SCL2 or SDA2                                     | 0                | 0.9   | 0                  | 0.6   | 0                | 0.4   | ns   |

| t <sub>PHL</sub>  | HIGH-to-<br>LOW<br>propagation<br>delav                          | from (input) SCL1 or SDA1 to<br>(output) SCL2 or SDA2                                  | 0                | 1.4   | 0                  | 1.1   | 0                | 0.7   | ns   |

| $V_{I(FN)} = 2$   |                                                                  | $V_{1L} = 0 \text{ V}; V_{T} = 2.5 \text{ V}; V_{M} = 0.75 \text{ V};$                 |                  |       |                    |       |                  |       |      |

| t <sub>PLH</sub>  | LOW-to-<br>HIGH<br>propagation<br>delay                          | from (input) SCL1 orSDA1 to<br>(output) SCL2 or SDA2                                   | 0                | 1     | 0                  | 0.6   | 0                | 0.4   | ns   |

| t <sub>PHL</sub>  | HIGH-to-<br>LOW<br>propagation<br>delay                          | from (input) SCL1 or SDA1 to<br>(output) SCL2 or SDA2                                  | 0                | 1.3   | 0                  | 1.3   | 0                | 0.8   | ns   |

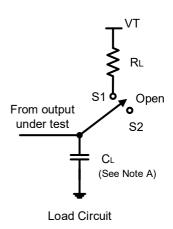

**Figure.2 Load Circuit for Outputs**

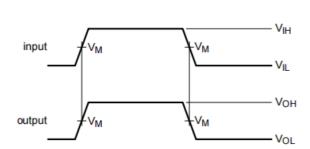

Figure 3. Parameter Measurement information

Notes: A. C<sub>L</sub> includes probe and jig capacitance.

- B. All input pluses are supplied by generators having the following characteristics: PRR≤10Mhz, Zo=50Ω, t,≤2ns, t,≤2ns.

- C. The outputs are measured one at a time, with one transition per measurement.

#### **Functional Description**

The RS7LS9306 is a dual bidirectional I<sup>2</sup>C-bus and SMBus voltage-level translator with an enable (EN) input, and is operational from 1.2 V to 3.3 V (VREF1) and 1.8 V to 5.5 V(VREF2).

The RS7LS9306 allows bidirectional voltage translations between 1.2 V and 5 V without the use of a direction pin. The low ON-state resistance (Ron) of the switch allows connections to be made with minimal propagation delay. When EN is HIGH, the translator switch is on, and the SCL1 and SDA1 I/O are connected to the SCL2 and SDA2 I/O respectively, allowing bidirectional data flow between ports. When EN is LOW, the translator switch is off, and a high- impedance state exists between ports.

The RS7LS9306 is not a bus buffer that provides both level translation and physically isolates to either side of the bus when both sides are connected. The RS7LS9306 only isolates both sides when the device is disabled and provides voltage level translation when active.

The RS7LS9306 can also be used to run two buses, one at 400kHz operating frequency and the other at 100 kHz operating frequency. If the two buses are operating at different frequencies, the 100 kHz bus must be isolated when the 400 kHz operation of the other bus is required. If the master is running at 400kHz, the maximum system operating frequency may be less than 400 kHz because of the delays added by the translator.

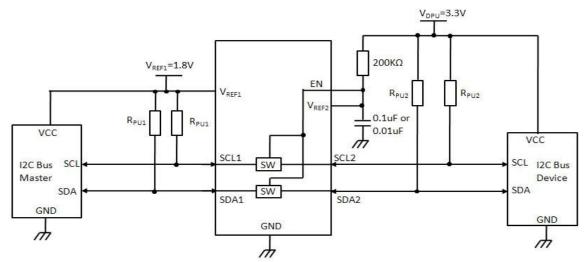

As with the standard I<sup>2</sup>C-bus system, pull-up resistors are required to provide the logic HIGH levels on the translator's bus. The RS7LS9306 has a standard open-collector configuration of the I<sup>2</sup>C-bus. The size of these pull-up resistors depends on the system, but each side of the translator must have a pull-up resistor. The device is designed to work with Standard-mode, Fast-mode and Fast mode Plus I<sup>2</sup>C-bus devices in addition to SMBus devices.

When the SDA1 or SDA2 port is LOW, the clamp is in the ON-state and a low resistance connection exists between the SDA1 and SDA2 ports. When the higher voltage is on the SDA2 port, and the SDA2 port is HIGH, the voltage on the SDA1 port is limited to the voltage set by VREF1. When the SDA1 port is HIGH, the SDA2 port is pulled to the drain pull-up supply voltage (VDPU) by the pull-up resistors. This functionality allows a seamless translation between higher and lower voltages selected by the user without the need for directional control. The SCL1/SCL2 channel also functions as the SDA1/SDA2 channel.

All channels have the same electrical characteristics and there is minimal deviation from one output to another in voltage or propagation delay. This is a benefit over discrete transistor voltage translation solutions, since the fabrication of the switch is symmetrical. The translator provides excellent ESD protection to lower voltage devices, and at the same time protects less ESD-resistant devices.

#### **Application Information**

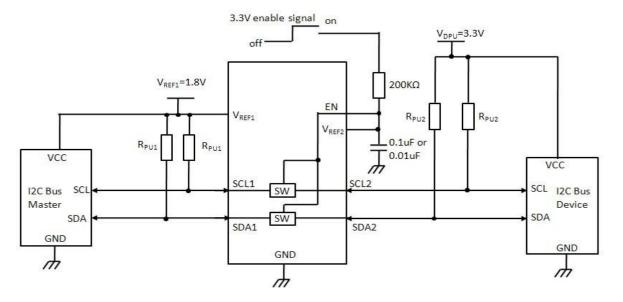

### **Open Drain Application**

For the bidirectional clamping configuration (higher voltage to lower voltage or lower voltage to higher voltage), the EN input must be connected to VREF2 and both pins pulled to high-side VDPU through a pull-up resistor (typically 200 k $\Omega$ ). This allows VREF2 to regulate the EN input. A filter capacitor on VREF2 is recommended.

Figure.3 Typical Open Drain Application Circuit (Switch Always Enabled)

Figure.4 Typical Open Drain Application Circuit (Switch Enabled Control)

## **Push Pull Application**

If used in push-pull system, the pull-up resistors on REF side are also needed. The data must be unidirectional or the outputs must be 3-stateable and be controlled by some direction-control mechanism to prevent high-to-low contentions in either direction.

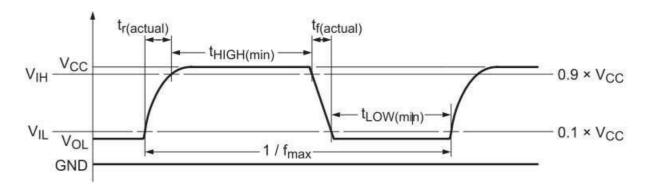

#### **MAX Frequency Application**

The maximum frequency is limited by the minimum pulse width LOW and HIGH as well as rise time and fall time.

$$f(\max) = \frac{1}{\text{tLOW(min)} + \text{tHIGH(min)} + \text{tr(actual)} + \text{tf(actual)}}$$

The rise and fall times are dependent upon translation voltages, the drive strength, the total node capacitance (CL) and the pull-up resistors (RPU) that are present on the bus. The node capacitance is the addition of the PCB trace capacitance and the device capacitance that exists on the bus.

Because of the dependency of the external components, PCB layout and the different device operating states the calculation of rise and fall times is complex and has several inflection points along the curve.

The main component of the rise and fall times is the RC time constant of the bus line when the device is in its two primary operating states: when device is in the ON state and it is low-impedance, the other is when the device is OFF isolating the A-side from the B-side.

There are some basic guidelines to follow that will help maximize the performance of the device:

- Keep trace length to a minimum by placing the RS7LS9306 close to the processor.

- The signal round trip time on trace should be shorter than the rise or fall time of signal to reduce reflections.

- The faster the edge of the signal, the higher the chance for ringing.

- The higher drive strength controlled by the pull-up resistor (up to 15 mA), the higher the frequency the device can use.

The system designer must design the pull-up resistor value based on external current drive strength and limit the node capacitance (minimize the wire, stub, connector and trace length) to get the desired operation frequency result.

10

RSM-DS-R-0024

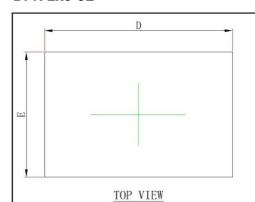

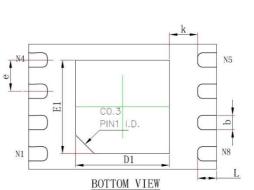

# **Package Information**

#### **DFN 2x3-8L**

| Cumbal | Dimensions In Millineters |       |  |  |  |  |

|--------|---------------------------|-------|--|--|--|--|

| Symbol | Min                       | Max   |  |  |  |  |

| Α      | 0.700                     | 0.800 |  |  |  |  |

| A1     | 0.000                     | 0.050 |  |  |  |  |

| A3     | 0.203F                    | REF.  |  |  |  |  |

| D      | 2.900                     | 3.100 |  |  |  |  |

| E      | 1.900                     | 2.100 |  |  |  |  |

| D1     | 1.400                     | 1.600 |  |  |  |  |

| E1     | 1.400                     | 1.600 |  |  |  |  |

| b      | 0.180                     | 0.280 |  |  |  |  |

| е      | 0.500BSC.                 |       |  |  |  |  |

| k      | 0.450REF.                 |       |  |  |  |  |

| L      | 0.250 0.350               |       |  |  |  |  |

Note: 1.All dimensions are in mm. 2.Dimensions exclude burrs, mold flash or protrusions. 3.Refer Jedec MO-220

TDFN 2X3-8L(ZE08) POD Rev.0

Raystar Microelectronics Technology Inc.

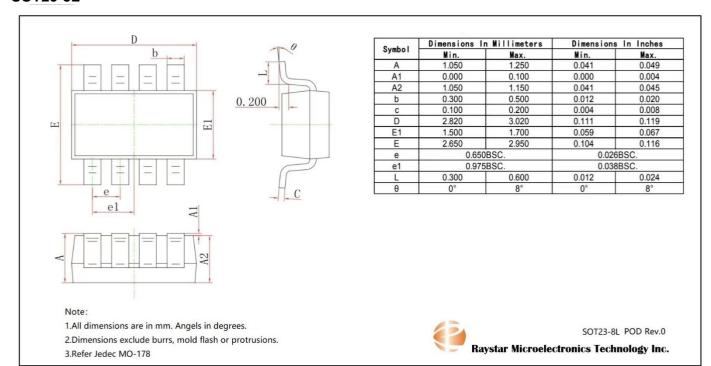

#### **SOT23-8L**

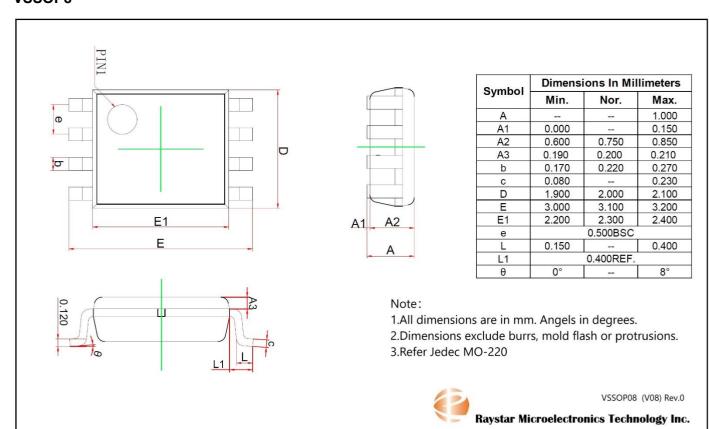

## VSSOP8

# **Revision History**

| Revision | Description                                                  | Date      |

|----------|--------------------------------------------------------------|-----------|

| 0.3      | Initial release                                              | 2023/4/23 |

| 1.0      | Modify the package description from 12-pin to 8-pin (Page 1) | 2023/9/26 |

| 1.1      | Update the temperature range and Ron spec                    | 2025/1/21 |

| 1.2      | ADD VSSOP8 package                                           | 2025/6/17 |