### **Features**

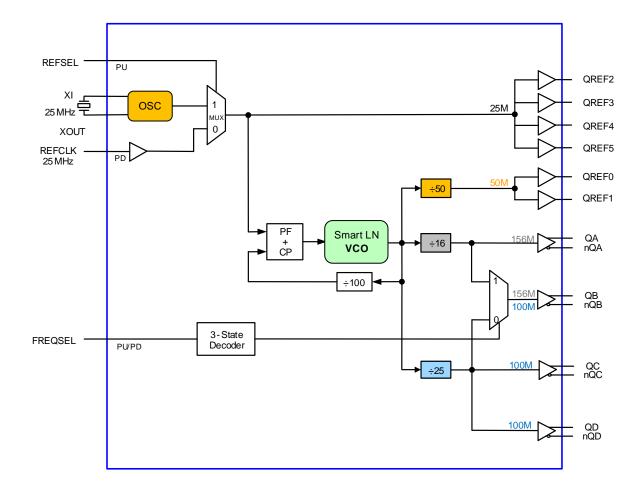

- Six single-ended LVCMOS outputs, 30Ω output impedance

- Four differential output pairs.

- One LVPECL (QA, nQA) output pair:156.25MHz

- One selectable LVPECL output pairs (QB, nQB): 100MHz 125MHz or 156.25MHz

- Two LP-HCSL output pairs: (QC, nQC and QD, nQD): 100MHz

- Selectable external crystal or single-ended input source

- Crystal oscillator interface designed for 25MHz, parallel resonant crystal

- VCO frequency: 2.5GHz

- RMS phase jitter @ 125MHz, using a 25MHz crystal (12kHz – 20MHz): 0.256ps (Typ.)

- Power supply noise rejection PSNR: -80dB

- 3.3V supply voltage

- -40°C to 85°C ambient operating temperature

- Lead-free (RoHS 6) packaging

# **Applications**

- PCI-e system

- Switch, Router

- 10Gb Ethernet network

- Communication system

- OTN

### **Description**

The RS2CG573 is a PLL based clock Generator for use in Ethernet applications. The device has optimal high clock frequency and low phase noise performance, combined with a low power consumption and high power supply noise rejection. Using RSM's latest PLL technology, the RS2CG573 achieves <0.3ps RMS phase jitter performance.

RS2CG573 can synthesize 100MHz, 125MHz, 156.25MHz and a low frequency 50MHz CPU clock from a single device. Four LVCMOS outputs also serve as additional buffering of the 25MHz crystal reference.

## **Order information**

| Part Number | Package  | Description |

|-------------|----------|-------------|

| RS2CG573ZDE | TQFN-40L | 6mmX6mm     |

# **Functional Block Diagram**

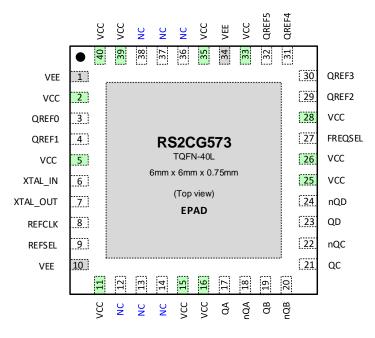

# **Pin Configuration**

# **Pin Descriptions**

| Pin No.                                          | Pin Name                      | Ту     | pe       | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|--------------------------------------------------|-------------------------------|--------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 10, 34                                        | VEE                           | Power  |          | Negative supply pins.                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2, 5, 11, 15,<br>16, 25,26, 28,<br>33,35, 39, 40 | Vcc                           | Power  |          | Power supply pins.<br>Pins 2, 28, 33 – power supply for the 25MHz LVCMOS<br>outputs<br>Pin 5 – power supply for the crystal oscillator<br>Pins 11, 15, 26, 35 – power supply for the dividers and<br>other core circuitry<br>Pin 16 – power supply for the differential LVPECL outputs<br>Pin 25 – power supply for the 50MHz LVCMOS output<br>Pin 39 – power supply for the digital logic<br>Pin 40 – power supply for the PLL |

| 3, 4                                             | QREF0, QREF1                  | Output |          | Single-ended outputs for 50MHz. 3.3V LVCMOS/LVTTL reference levels.                                                                                                                                                                                                                                                                                                                                                             |

| 29,30,31,32                                      | QREF2, QREF3,<br>QREF4, QREF5 | Output |          | Single-ended outputs for 25MHz. 3.3V LVCMOS/LVTTL reference levels.                                                                                                                                                                                                                                                                                                                                                             |

| 6,7                                              | XTAL_IN, XTAL_OUT             | Input  |          | Parallel resonant crystal interface. XTAL_OUT is the output, XTAL_IN is the input.                                                                                                                                                                                                                                                                                                                                              |

| 8                                                | REFCLK                        | Input  | Pulldown | Single-ended LVCMOS/LVTTL reference clock input.                                                                                                                                                                                                                                                                                                                                                                                |

| 9                                                | REFSEL                        | Input  | Pullup   | Reference select pin. When HIGH, selects crystal. When LOW, selects REFCLK. LVCMOS/LVTTL interface levels.                                                                                                                                                                                                                                                                                                                      |

| 12,13,14,36,<br>37,38                            | NC                            |        |          | No connect.                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17, 18                                           | QA, nQA                       | Output |          | 156.25MHz differential output. LVPECL interface levels.                                                                                                                                                                                                                                                                                                                                                                         |

| 19, 20                                           | QB, nQB                       | Output |          | 100MHz,125MHz or 156.25MHz differential output.<br>LVPECL interface levels.                                                                                                                                                                                                                                                                                                                                                     |

| Pin No. | Pin Name | Туре   |        | Description                                                    |

|---------|----------|--------|--------|----------------------------------------------------------------|

| 21, 22  | QC, nQC  | Output |        | 100MHz differential output. LP-HCSL interface levels.          |

| 23, 24  | QD, QD0  | Output |        | 100MHz differential output. LP-HCSL interface levels.          |

| 27      | FREQSEL  | Input  | Pullup | Frequency select pin. See Table. LVCMOS/LVTTL interface level. |

# **Pin Characteristics**

| Symbol              | Parameter                                     |           | Test Conditions        | MIN | ТҮР | MAX | Units |

|---------------------|-----------------------------------------------|-----------|------------------------|-----|-----|-----|-------|

| C <sub>IN</sub>     | Input Capacitance                             |           | Crystal Not Included   |     | 2   |     | pF    |

| C <sub>PD</sub>     | Power Dissipation Capacitance<br>(per output) | QREF[0:5] | V <sub>CC</sub> = 3.6V |     | 6   |     | pF    |

| R <sub>PULLUP</sub> | Input Pullup Resistor                         |           |                        |     | 51  |     | kΩ    |

| RPULLDOWN           | Input Pulldown Resistor                       |           |                        |     | 51  |     | kΩ    |

| ROUT                | Output Impedance                              | QREF[0:5] |                        |     | 30  |     | Ω     |

# **Function Tables**

#### **REFSEL Function table**

| REFSEL      | Input Source |  |  |  |  |  |

|-------------|--------------|--|--|--|--|--|

| 0           | REFCLK       |  |  |  |  |  |

| 1 (default) | OSC          |  |  |  |  |  |

#### FREQSEL Function Table

|         | Output Frequency (MHz) |

|---------|------------------------|

| FREQSEL | QB, nQB                |

| 0       | 100                    |

| М       | 125                    |

| 1       | 156.25 (Default)       |

### **Absolute Maximum Ratings**

Exposure to absolute Max rating conditions for extended periods may affect product reliability. Stresses beyond those listed under Absolute Max Ratings may cause permanent damage to the device. These ratings are stress specifications only. Functional operation of product at these conditions or any conditions beyond those listed in the DC Characteristics or AC Characteristics is not implied.

| Parameter                                                                 | MIN  | MAX                   | Units |

|---------------------------------------------------------------------------|------|-----------------------|-------|

| Supply Voltage, VCC                                                       | 3    | 3.6                   | V     |

| Inputs                                                                    | -0.5 | V <sub>CC</sub> + 0.5 | V     |

| XTAL_IN                                                                   | 0    | 2                     |       |

| Outputs, IO (LVCMOS)                                                      | -0.5 | VCC + 0.5             | V     |

| Outputs, IO (LVPECL)<br>Continuous Current<br>Surge Current Surge Current |      | 50<br>100             | mA    |

| Package Thermal Impedance, θJA                                            |      | 37.7                  | °C /W |

| Max Junction Temperature, TJMAX                                           |      | 150                   | °C    |

| Storage Temperature, TSTG                                                 | 65   | 150                   | °C    |

### **Recommended Operating Condition**

| Symbol | Parameter               | MIN | ТҮР | MAX | Units |

|--------|-------------------------|-----|-----|-----|-------|

| TA     | Ambient air temperature | -40 |     | 85  | °C    |

| ТJ     | Junction temperature    |     |     | 125 | °C    |

Note 1: It is the user's responsibility to ensure that device junction temperature remains below the Max allowed; Note 2: All conditions in the table must be met to guarantee device functionality.

Note3: The device is verified to the Max operating junction temperature through simulation.

### **DC Electrical Characteristics**

### Power Supply DC Characteristics, V<sub>CC</sub> = 3.3V $\pm$ 0.3V, V<sub>EE</sub> = 0V, T<sub>A</sub> = -40°C to 85°C

| Symbol | Parameter            | Test Conditions | MIN | ТҮР | MAX | Units |

|--------|----------------------|-----------------|-----|-----|-----|-------|

| Vcc    | Power Supply Voltage |                 | 3.0 | 3.3 | 3.6 | V     |

| IEE    | Power Supply Current | No Load         |     |     | 250 | mA    |

### LVCMOS/LVTTL DC Characteristics, VCC = $3.3V \pm 0.3V$ , TA = $-40^{\circ}$ C to $85^{\circ}$ C

| Symbol      | Paran                   | neter              | Test Conditions          | MIN                      | ТҮР | MAX                      | Units |

|-------------|-------------------------|--------------------|--------------------------|--------------------------|-----|--------------------------|-------|

| VIH         | Input High Voltage      | REFSEL             |                          | 2                        |     | V <sub>CC</sub> + 0.3    | V     |

| ٩H          | Input High Voltage      | FREQSEL            |                          | V <sub>CC</sub> - 0.4    |     |                          | V     |

| VIL         |                         | REFSEL             |                          | -0.3                     |     | 0.8                      | V     |

| ۷IL         | Input Low Voltage       | FREQSEL            |                          |                          |     | 0.4                      | V     |

| $\vee_{IM}$ | Input Medium<br>Voltage | FREQSEL            |                          | V <sub>CC</sub> /2 - 0.1 |     | V <sub>CC</sub> /2 + 0.1 | V     |

| ЧH          | Input High Current      | REFCLK,<br>FREQSEL | VCC = 3.6V<br>VIN = 3.6V |                          |     | 150                      | μΑ    |

|             |                         | REFSEL             | VCC = 3.6V<br>VIN = 3.6V |                          |     | 5                        | μA    |

| 1           |                         | REFCLK             | VCC = 3.6V<br>VIN = 0V   | -5                       |     |                          | μA    |

| ΙL          | Input Low Current       | REFSEL,<br>FREQSEL | VCC = 3.6V<br>VIN = 0V   | -150                     |     |                          | μA    |

| VOH         | Output High Voltage;    | Note 1             | $V_{CC} = 3.3V \pm 0.3V$ | 2.3                      |     |                          | V     |

| VOL         | Output Low Voltage;     | Note 1             | $V_{CC} = 3.3V \pm 0.3V$ |                          |     | 0.8                      | V     |

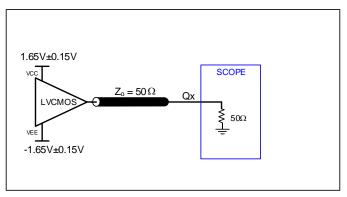

NOTE 1: Outputs terminated with 500 to Vcc/2. See Parameter Measurement Information, Output Load Test Circuit diagrams.

### LVPECL DC Characteristics, $V_{CC}$ = 3.3V ± 0.3V, $V_{EE}$ = 0V, $T_A$ = -40°C to 85°C

| Symbol | Parameter                         | Test Conditions | MIN                   | TYP | MAX                   | Units |

|--------|-----------------------------------|-----------------|-----------------------|-----|-----------------------|-------|

| VOH    | Output High Voltage; Note 1       |                 | V <sub>CC</sub> – 1.4 |     | V <sub>CC</sub> – 0.8 | V     |

| VOL    | Output Low Voltage; Note 1        |                 | VCC - 2.0             |     | VCC - 1.6             | V     |

| VSWING | Peak-to-Peak Output Voltage Swing |                 | 0.6                   |     | 1.0                   | V     |

**Note 1:** Outputs terminated with 50ohm  $V_{CC} - 2V$

#### **Crystal Characteristics**

| Parameter                          | Test Conditions | MIN         | ТҮР | MAX | Units |

|------------------------------------|-----------------|-------------|-----|-----|-------|

| Mode of Oscillation                |                 | Fundamental |     |     |       |

| Frequency                          |                 |             | 25  |     | MHz   |

| Equivalent Series Resistance (ESR) |                 |             |     | 50  | Ω     |

| Shunt Capacitance                  |                 |             |     | 7   | pF    |

### **AC Electrical Characteristics**

### LVPECL AC Characteristics, V<sub>CC</sub> = 3.3V $\pm$ 0.3V, V<sub>EE</sub> = 0V, T<sub>A</sub> = -40°C to 85°

| Symbol                          | Parameter                           |                          | Test Conditions                                                               | MIN | ТҮР   | MAX    | Units |

|---------------------------------|-------------------------------------|--------------------------|-------------------------------------------------------------------------------|-----|-------|--------|-------|

| f <sub>IN</sub>                 | Input F                             | requency                 |                                                                               |     | 25    |        | MHz   |

| fout                            | Output F                            | Frequency                |                                                                               | 100 |       | 156.25 | MHz   |

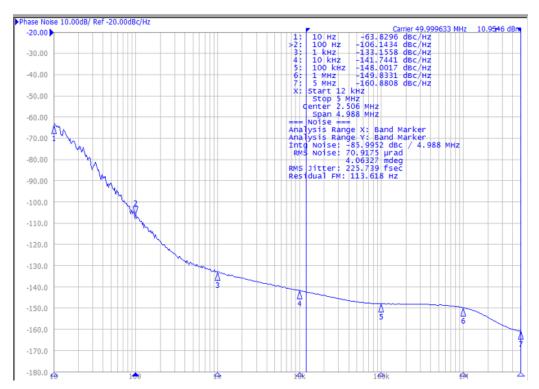

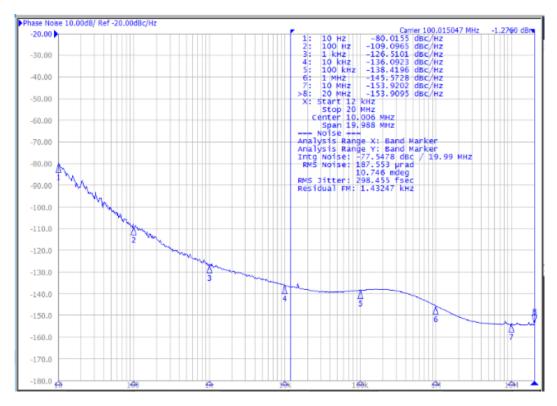

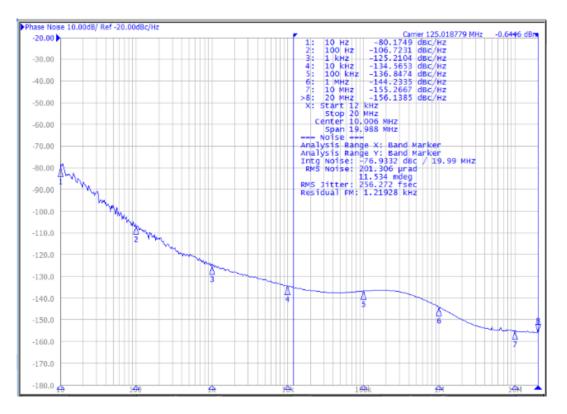

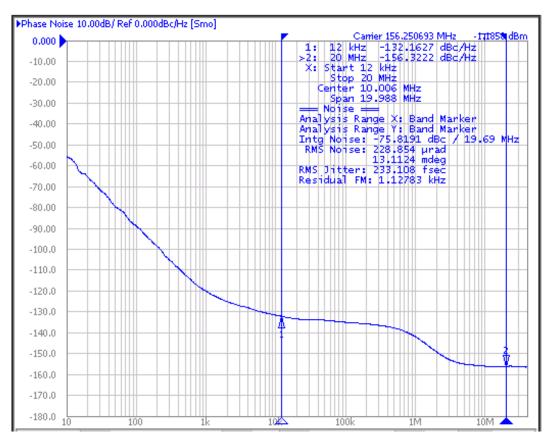

|                                 |                                     |                          | 156.25MHz f <sub>OUT</sub> , 25MHz crystal<br>Integration Range:12kHz – 20MHz |     | 0.233 |        | ps    |

| tjit(0)                         | RMS Phase Jitter<br>(Random) Note 1 |                          | 125MHz f <sub>OUT</sub> , 25MHz crystal<br>Integration Range: 12kHz – 20MHz   |     | 0.260 |        | ps    |

|                                 |                                     |                          | 100MHz f <sub>OUT</sub> , 25MHz crystal<br>Integration Range: 12kHz – 20MHz   |     | 0.28  |        | ps    |

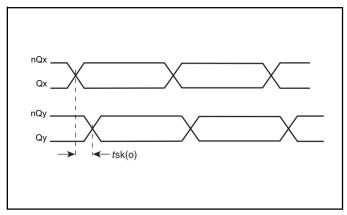

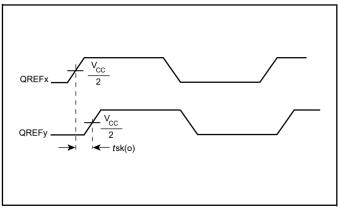

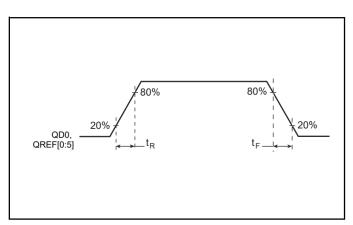

| tsk(o)                          | Output Skew; Note 2, 3              |                          | Measured on the Rising Edge                                                   |     |       | 40     | ps    |

| PSNR                            | Power Supply<br>Noise Reduction     | Pin40 (V <sub>CC</sub> ) | From DC to 8MHz                                                               |     | -75   |        | dB    |

| RONK                            |                                     | Pin40 (VCC)              | From DC to 3MHz                                                               |     | -80   |        | dB    |

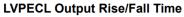

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time               |                          | 20% to 80%                                                                    | 150 |       | 550    | ps    |

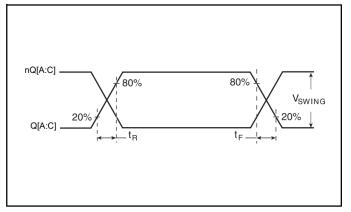

| ODC                             | Output Duty Cycle                   |                          |                                                                               | 48  |       | 52     | %     |

Note: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established

when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet

specifications after thermal equilibrium has been reached under these conditions

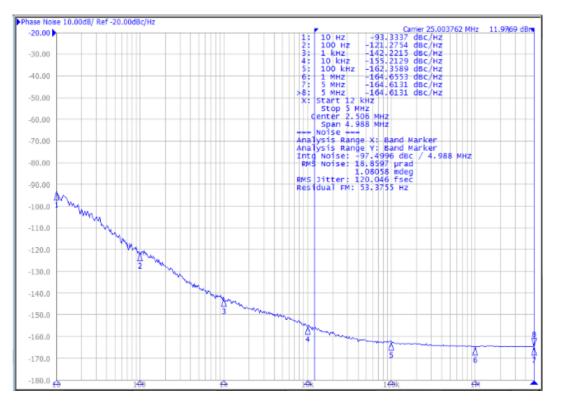

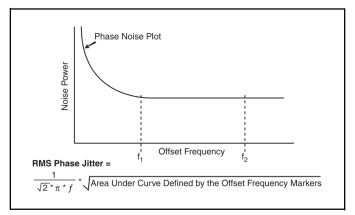

Note 1: Refer to the Phase Noise Plot.

Note 2: This parameter is defined in accordance with JEDEC Standard 65.

Note 3: Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at the differential crosspoints

#### AC Characteristics for Single Side Band Power Levels (LVPECL Outputs)

$V_{CC} = 3.3V \pm 0.3V, V_{EE} = 0V, T_{A} = 25^{\circ}C$

| Symbol                | Parameter                                            | Test Conditions | MIN | ТҮР  | MAX | Units  |

|-----------------------|------------------------------------------------------|-----------------|-----|------|-----|--------|

| Φ <sub>N</sub> (1k)   | Single-side band phase noise,<br>1kHz from Carrier   |                 |     | -122 |     | dBc/Hz |

| Φ <sub>N</sub> (10k)  | Single-side band phase noise,<br>10kHz from Carrier  |                 |     | -133 |     | dBc/Hz |

| Φ <sub>N</sub> (100k) | Single-side band phase noise,<br>100kHz from Carrier | 156 25MHz       |     | -136 |     | dBc/Hz |

| Φ <sub>N</sub> (1M)   | Single-side band phase noise,<br>1MHz from Carrier   | 156.25MHz       |     | -142 |     | dBc/Hz |

| Φ <sub>N</sub> (10M)  | Single-side band phase noise, 10MHz from Carrier     |                 |     | -155 |     | dBc/Hz |

| Φ <sub>N</sub> (20M)  | Single-side band phase noise, 20MHz from Carrier     |                 |     | -156 |     | dBc/Hz |

| Φ <sub>N</sub> (1k)   | Single-side band phase noise,<br>1kHz from Carrier   | 125MHz          |     | -125 |     | dBc/Hz |

| Φ <sub>N</sub> (10k)  | Single-side band phase noise,<br>10kHz from Carrier  | 1231/1172       |     | -135 |     | dBc/Hz |

| Φ <sub>N</sub> (100k) | Single-side band phase noise,<br>100kHz from Carrier |        | -138 | dBc/Hz |

|-----------------------|------------------------------------------------------|--------|------|--------|

| Φ <sub>N</sub> (1M)   | Single-side band phase noise,<br>1MHz from Carrier   |        | -144 | dBc/Hz |

| Φ <sub>N</sub> (10M)  | Single-side band phase noise, 10MHz from Carrier     |        | -155 | dBc/Hz |

| Φ <sub>N</sub> (20M)  | Single-side band phase noise, 20MHz from Carrier     |        | -156 | dBc/Hz |

| Φ <sub>N</sub> (1k)   | Single-side band phase noise,<br>1kHz from Carrier   | 100MHz | -126 | dBc/Hz |

| Φ <sub>N</sub> (10k)  | Single-side band phase noise,<br>10kHz from Carrier  |        | -136 | dBc/Hz |

| Φ <sub>N</sub> (100k) | Single-side band phase noise,<br>100kHz from Carrier |        | -139 | dBc/Hz |

| Φ <sub>N</sub> (1M)   | Single-side band phase noise,<br>1MHz from Carrier   |        | -145 | dBc/Hz |

| Φ <sub>N</sub> (10M)  | Single-side band phase noise,<br>10MHz from Carrier  |        | -154 | dBc/Hz |

| Φ <sub>N</sub> (20M)  | Single-side band phase noise,<br>20MHz from Carrier  |        | -154 | dBc/Hz |

Note: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

#### **LVCMOS AC Characteristics,** $V_{CC} = 3.3V \pm 0.3V$ , $T_A = -40^{\circ}C$ to $85^{\circ}C$

| Symbol                          | Parameter                       |            | Test Conditions                                                          | MIN | ТҮР   | MAX | Units |

|---------------------------------|---------------------------------|------------|--------------------------------------------------------------------------|-----|-------|-----|-------|

| f <sub>IN</sub>                 | Input Freq                      | uency      |                                                                          |     | 25    |     | MHz   |

| fout                            | Output Fre                      | quency     |                                                                          | 25  |       | 50  | MHz   |

| 4::4(0)                         | RMS Phase Jitter (Random)       |            | 25MHz fOUT, 25MHz crystal Integration<br>Range:12kHz – 5MHz              |     | 0.2   |     | ps    |

| tjit( <del>0</del> )            | tjit(θ) NOTE 1                  |            | 50MHz f <sub>OUT</sub> , 25MHz crystal<br>Integration Range:12kHz – 5MHz |     | 0.220 |     | ps    |

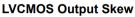

| tsk(o)                          | Output Skew;<br>NOTE 2, 3       | QREF[0:5]  | Measured on the Rising Edge                                              |     |       | 50  | ps    |

| PSNR                            | Power Supply<br>Noise Reduction | Pin4,(VCC) | From DC to 6.25MHz                                                       |     | -80   |     | dB    |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time           |            | 20% to 80%                                                               |     | 700   |     | ps    |

| ODC                             | Output Dut                      | y Cycle    |                                                                          | 48  |       | 52  | %     |

Note: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions

Note 1: Refer to the Phase Noise Plot.

Note 2: This parameter is defined in accordance with JEDEC Standard 65.

Note 3: Defined as skew between outputs at the same supply voltage and with equal load conditions. Measured at V<sub>CC</sub>/2.

### AC Characteristics for Single Side Band Power Levels (LVCMOS Outputs)

$V_{CC} = 3.3V \pm 0.3V$ ,  $V_{EE} = 0V$ ,  $T_{A} = 25^{\circ}C$

| Symbol                | Parameter                                            | Test Conditions | MIN | TYP  | MAX | Units  |

|-----------------------|------------------------------------------------------|-----------------|-----|------|-----|--------|

| Φ <sub>N</sub> (1k)   | Single-side band phase noise,<br>1kHz from Carrier   |                 |     | -136 |     | dBc/Hz |

| Φ <sub>N</sub> (10k)  | Single-side band phase noise, 10kHz from Carrier     |                 |     | -146 |     | dBc/Hz |

| Φ <sub>N</sub> (100k) | Single-side band phase noise, 100kHz from Carrier    | 25MHz           |     | -150 |     | dBc/Hz |

| Ф <sub>N</sub> (1М)   | Single-side band phase noise,<br>1MHz from Carrier   |                 |     | -156 |     | dBc/Hz |

| Φ <sub>N</sub> (5M)   | Single-side band phase noise,<br>5MHz from Carrier   |                 |     | -164 |     | dBc/Hz |

| Φ <sub>N</sub> (1k)   | Single-side band phase noise,<br>1kHz from Carrier   |                 |     | -133 |     | dBc/Hz |

| Ф <sub>N</sub> (10k)  | Single-side band phase noise, 10kHz from Carrier     |                 |     | -141 |     | dBc/Hz |

| Φ <sub>N</sub> (100k) | Single-side band phase noise,<br>100kHz from Carrier | 50MHz           |     | -148 |     | dBc/Hz |

| Ф <sub>N</sub> (1М)   | Single-side band phase noise,<br>1MHz from Carrier   |                 |     | -149 |     | dBc/Hz |

| Φ <sub>N</sub> (5M)   | Single-side band phase noise,<br>5MHz from Carrier   |                 |     | -160 |     | dBc/Hz |

Note: Electrical parameters are guaranteed over the specified ambient operating temperature range, which is established when the device is mounted in a test socket with maintained transverse airflow greater than 500 lfpm. The device will meet specifications after thermal equilibrium has been reached under these conditions.

### Typical Phase Noise at 50MHz (LVCMOS Output)

#### Typical Phase Noise at 25MHz (LVCMOS Output)

#### Typical Phase Noise at 100MHz (LVPECL Output)

#### Typical Phase Noise at 125MHz (LVPECL Output)

#### Typical Phase Noise at 156.25MHz (LVPECL Output)

### **Parameter Measurement Information**

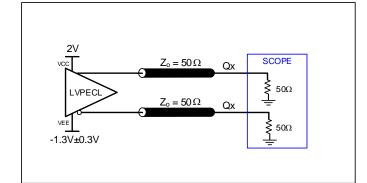

#### LVPECL Output Load AC Test Circuit

**Phase Jitter**

LVPECL Output Skew

#### LVCMOS Output Load AC Test Circuit

LVCMOS Output Duty Cycle/Pulse Width/Period

LVPECL Output Duty Cycle/Pulse Width/Period

### **Applications Information**

### **Overdriving the XTAL Interface**

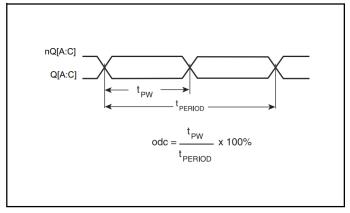

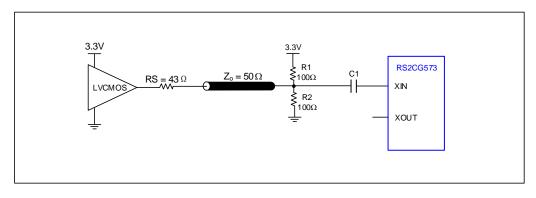

The XTAL\_IN input can accept a single-ended LVCMOS signal through an AC coupling capacitor. A general interface diagram is shown in *Figure 1A*. The XTAL\_OUT pin can be left floating. The maximum amplitude of the input signal should not exceed 2V and the input edge rate can be as slow as 10ns. This configuration requires that the output impedance of the driver (Ro) plus the series resistance (Rs) equals the transmission line impedance. In addition, matched termination at the crystal input will attenuate the signal in half. This can be done in one of two ways. First, R1 and R2 in parallel should equal the transmission line impedance. For most 500hm applications, R1 and R2 can be 100 . This can also be accomplished by removing R1 and making R2 500hm . By overdriving the crystal oscillator, the device will be functional, but note, the device performance is guaranteed by using a quartz crystal.

Figure 1A. General Diagram for LVCMOS Driver to XTAL Input Interface

Figure 1B. General Diagram for LVPECL Driver to XTAL Input Interface

### **EPAD Thermal Release Path**

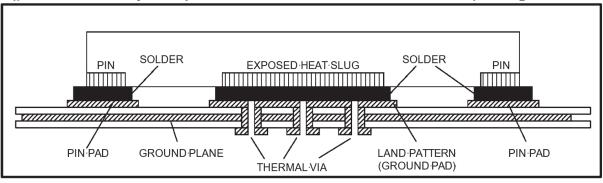

In order to maximize both the removal of heat from the package and the electrical performance, a land pattern must be incorporated on the Printed Circuit Board (PCB) within the footprint of the package corresponding to the exposed metal pad or exposed heat slug on the package, as shown in *Figure 2*. The solderable area on the PCB, as defined by the solder mask, should be at least the same size/shape as the exposed pad/slug area on the package to maximize the thermal/electrical performance. Sufficient clearance should be designed on the PCB between the outer edges of the land pattern and the inner edges of pad pattern for the leads to avoid any shorts.

While the land pattern on the PCB provides a means of heat transfer and electrical grounding from the package to the board through a solder joint, thermal vias are necessary to effectively conduct from the surface of the PCB to the ground plane(s). The land pattern must be connected to ground through these vias. The vias act as "heat pipes". The number of vias (i.e. "heat pipes") are application specific and dependent upon the package power dissipation as well as electrical conductivity requirements. Thus, thermal and electrical analysis and/or testing are recommended to determine the minimum number needed. Maximum thermal and electrical performance is achieved when an array of vias is incorporated in the land pattern. It is recommended to use as many vias connected to ground as possible. It is also recommended that the via diameter should be 12 to 13mils (0.30 to 0.33mm) with 1oz copper via barrel plating. This is desirable to avoid any solder wicking inside the via during the soldering process which may result in voids in solder between the exposed pad/slug and the thermal land. Precautions should be taken to eliminate any solder voids between the exposed heat slug and the land pattern. Note: These recommendations are to be used as a guideline only. For further information, please refer to the Application Note on the Surface Mount Assembly of Amkor's Thermally/ Electrically Enhance Leadframe Base Package, Amkor Technology.

#### Figure 2 P.C. Assembly for Exposed Pad Thermal Release Path – Side View (drawing not to scale)

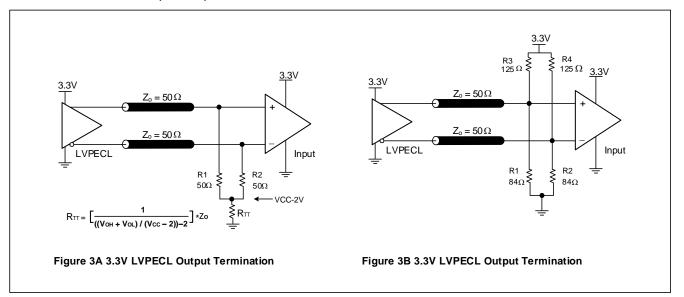

#### **Termination for 3.3V LVPECL Outputs**

The clock layout topology shown below is a typical termination for LVPECL outputs. The two different layouts mentioned are recommended only as guidelines.

The differential outputs are low impedance follower outputs that generate ECL/LVPECL compatible outputs.

Therefore, terminating resistors (DC current path to ground) or current sources must be used for functionality. These outputs are designed to drive 500hm transmission lines. Matched impedance techniques should be used to maximize operating frequency and minimize signal distortion.

Figures 3A and 3B show two different layouts which are recommended only as guidelines. Other suitable clock layouts may exist and it would be recommended that the board designers simulate to guarantee compatibility across all printed circuit and clock component process variations.

#### **Recommendations for Unused Input and Output Pins**

#### Inputs

#### **REFCLK Input**

For applications not requiring the use of the reference clock, it can be left floating. Though not required, but for additional protection, a  $1k\Omega$  resistor can be tied from the REFCLK to ground.

#### **Crystal Inputs**

For applications not requiring the use of the crystal oscillator input, both XTAL\_IN and XTAL\_OUT can be left floating. Though not required, but for additional protection, a  $1k\Omega$  resistor can be tied from XTAL\_IN to ground.

#### LVCMOS Control Pins

All control pins have internal pull-ups or pull-downs; additional resistance is not required but can be added for additional protection. A  $1k\Omega$  resistor can be used.

#### Outputs

#### LVCMOS Outputs

All unused LVCMOS output can be left floating. There should be no trace attached.

#### LVPECL Outputs

All unused LVPECL outputs can be left floating. We recommend that there is no trace attached. Both sides of the differential output pair should either be left floating or terminated

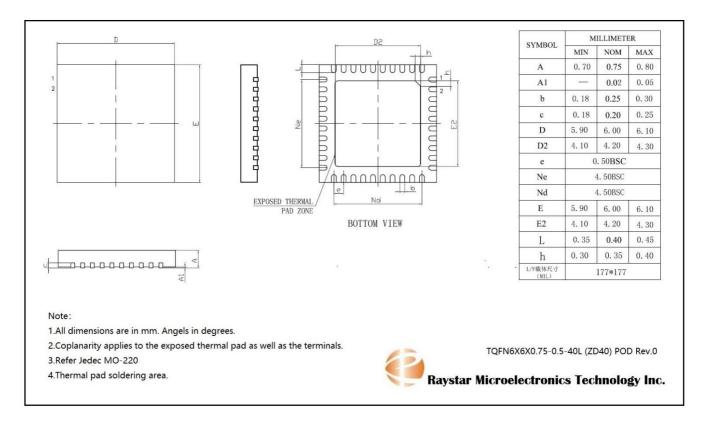

### **Package information**

### TQFN-40L

# **Revision History**

| Revision | Description     | Date       |

|----------|-----------------|------------|

| 0.9      | Preliminary     | 2025/2/12  |

| 1.0      | Initial release | 2025/03/04 |

|          |                 |            |