### **Features**

- Selectable reference inputs support either single-ended or differential or XTAL

- 4 Differential Outputs With 2 Banks

- User Configurable Output Signaling Standard for each bank: LVDS or LVPECL or HCSL

- LVCMOS reference Output up to 250MHz

- Up to 1.5GHz output frequency for differential outputs (LVDS,LVPECL)

- Ultralow additive phase jitter: < 20fs RMS (typical value in differential 156.25MHz, 12KHz to 20MHz integration range)

- Low skew between outputs within banks (< 40ps)

- Low delay from input to output (< 0.9ns)

- Pin-Controlled Configuration

- Spread-spectrum tolerant

- Vcc Core Supply: 3.3V ±5% / 2.5V ±5%

- V<sub>CCO</sub> Output Supplies: 3.3V ±5% / 2.5V ±5%

V<sub>CCO</sub> can't be greater than VCC (V<sub>CCO</sub> ≤ V<sub>CC</sub>)

- Separate Input output supply voltage for level shifting

- -40°C to 125°C ambient operating temperature

- AEC-Q 100 qualified, Automotive Grade 1 support; PPAP capable, and manufactured in IATF 16949 certified facilities

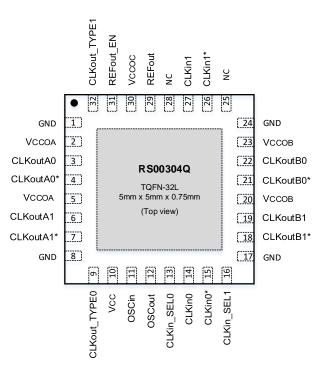

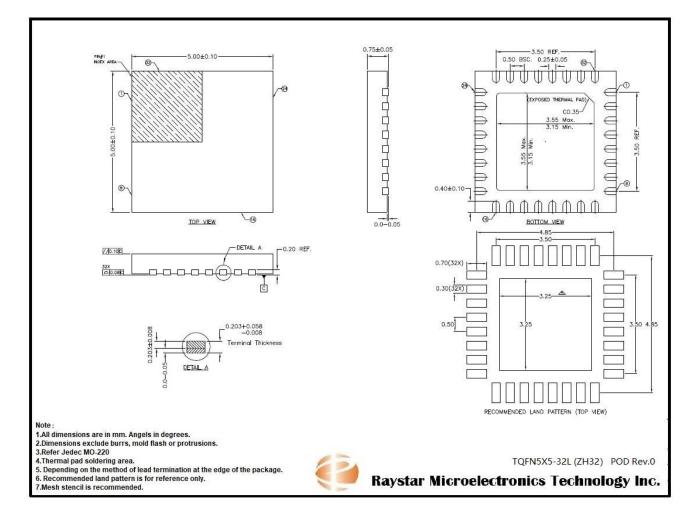

- Package: 32-lead TQFN (5 mm × 5mm)

## **Applications**

- PCle Gen1~Gen5

- Clock Distribution and Level Translation for ADCs, DACs, Multi-Gigabit Ethernet, XAUI, Fibre Channel, SATA/SAS, SONET/SDH, CPRI, High-Frequency Backplanes

- Switches, Routers, Line Cards, Timing Cards

- Servers, Computing

- Remote Radio Units and Baseband Units

- ADAS

### Description

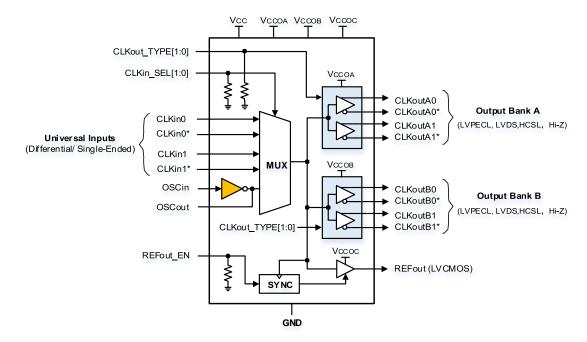

The RS00304Q is a 1.5GHz 4-output differential fan out buffer intended for high-frequency, low-jitter clock/data distribution and level translation.

The input clock can be selected from two universal inputs or one crystal input. The selected input clock is distributed to two banks of 2 differential outputs and one LVCMOS output. The differential output banks can be mutually configured as LVPECL, LVDS, HCSL drivers, or disabled. The LVCMOS output has a synchronous enable input for runt-pulse-free operation when enabled or disabled. The RS00304Q operates from a 3.3V/2.5V core supply and 3 independent 3.3V/2.5V output supplies.

The RS00304Q provides high performance, versatility, and power efficiency, making it ideal for replacing fixed-output buffer devices while increasing timing margin in the system.

## **Ordering Information**

| Part Number | Package  | Description    |

|-------------|----------|----------------|

| RS00304QZHE | TQFN-32L | 5mmx5mmx0.75mm |

Notes: E = Pb-free and Green

## **Block Diagram**

## **Pin Configuration**

### **Pin Description**

| Pin No.        | Pin Name                      | Туре | Description                                                                                  |

|----------------|-------------------------------|------|----------------------------------------------------------------------------------------------|

| DAP            | DAP                           | GND  | Die Attach Pad.<br>Connect to the PCB ground plane for heat dissipation.                     |

| 1, 8<br>17, 24 | GND                           | GND  | Ground                                                                                       |

| 2, 5           | V <sub>CCOA</sub>             | Р    | Power supply for Bank A Output buffers. $V_{CCOA}$ operates at 3.3V or 2.5V.                 |

| 3, 4           | CLKoutA0,<br>CLKoutA0*        | 0    | Differential clock output A0.<br>Output type set by CLKoutA_TYPE pins.                       |

| 6, 7           | CLKoutA1,<br>CLKoutA1*        | 0    | Differential clock output A1.<br>Output type set by CLKoutA_TYPE pins.                       |

| 9, 32          | CLKout_TYPE0,<br>CLKout_TYPE1 | I    | Bank A and Bank B output buffer type selection pins [2]                                      |

| 10, 28         | Vcc                           | Р    | Power supply for Core and Input Buffer blocks. The $V_{CC}$ supply operates at 3.3V or 2.5V. |

| 11             | OSCin                         | I    | Input for crystal. Can also be driven by a XO, TCXO, or other external single-ended clock.   |

| 12             | OSCout                        | 0    | Output for crystal. Leave OSCout floating if OSCin is driven by a single-ended clock.        |

| 13, 16         | CLKin_SEL0,<br>CLKin_SEL1     | I    | Clock input selection pins. <sup>[2]</sup>                                                   |

| 14, 15         | CLKin0, CLKin0*               | I    | Universal clock input 0 (differential/single-ended)                                          |

| 18, 19         | CLKoutB1*,<br>CLKoutB1        | 0    | Differential clock output B1.<br>Output type set by CLKoutB_TYPE pins.                       |

| 20, 23         | V <sub>CCOB</sub>             | Р    | Power supply for Bank B Output buffers. $V_{CCOB}$ operates at 3.3V or 2.5V.                 |

| 21, 22         | CLKoutB0*,<br>CLKoutB0        | 0    | Differential clock output B0.<br>Output type set by CLKoutB_TYPE pins.                       |

| 25             | NC                            | -    | Not connected internally.                                                                    |

| 26, 27         | CLKin1*,CLKin1                | I    | Universal clock input 1 (differential/single-ended)                                          |

| 29             | REFout                        | 0    | LVCMOS reference output.<br>Enable output by pulling REFout_EN pin high.                     |

| 30             | Vccoc                         | Р    | Power supply for REFout buffer.<br>V <sub>CCOC</sub> operates at 3.3V or 2.5V.               |

| 31             | REFout_EN                     | I    | REFout enable input. Enable signal is internally synchronized to selected clock input.       |

Note

[1] Any unused output pins should be left floating with minimum copper length (see note in Clock Outputs), or properly terminated if connected to a transmission line, or disabled/Hi-Z if possible. See Clock Outputs for output configuration and Termination and Use of Clock Drivers for output interface and termination techniques.

[2] CMOS control input with internal pull-down resistor.

## **Function Table**

Table 1. Input Selection

| CLKin_SEL1 | CLKin_SEL0 | SELECTED INPUT  |

|------------|------------|-----------------|

| 0          | 0          | CLKin0, CLKin0* |

| 0          | 1          | CLKin1, CLKin1* |

| 1          | Х          | OSCin           |

Table 2. Differential Output Buffer Type Selection

| CLKout_ TYPE1 | Cout_TYPE1 CLKout_TYPE0 CLKoutX BUFFER |                 |  |  |

|---------------|----------------------------------------|-----------------|--|--|

| 0 0           |                                        | LVPECL          |  |  |

| 0             | 1 LVDS                                 |                 |  |  |

| 1             | 0 HCSL                                 |                 |  |  |

| 1             | 1                                      | Disabled (Hi-Z) |  |  |

#### Table 3. Reference output Enable

| REFout_EN | EN REFout STATE |  |  |

|-----------|-----------------|--|--|

| 0         | Disabled (Hi-Z) |  |  |

| 1         | Enabled         |  |  |

#### Table 4. CLKin Input vs. Output States

| STATE of SELECTED CLKin                    | STATE of ENABLED OUTPUTS           |

|--------------------------------------------|------------------------------------|

| CLKinX and CLKinX* inputs floating         | Logic low                          |

| CLKinX and CLKinX* inputs shorted together | Not Supported. Output is Undefined |

| CLKin logic low                            | Logic low                          |

| CLKin logic high                           | Logic high                         |

### **Absolute Maximum Ratings**

| Storage Temperature<br>Ambient Temperature<br>Junction Temperature<br>Supply Voltage to Ground<br>Input Voltage<br>Clock Output Voltage<br>Latch Up | 40°C to +125°C<br>+150°C<br> |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| ESD, HBM                                                                                                                                            |                              |

| Clock Output Voltage<br>Latch Up                                                                                                                    | –0.5V to VCC+0.5V<br>200mA   |

#### Note:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

### **Thermal Information**

| Symbol | Description                            | Test<br>Conditions                     | MIN | ТҮР  | MAX | Unit |

|--------|----------------------------------------|----------------------------------------|-----|------|-----|------|

| θJc    | Junction to case thermal resistance    | nction to case thermal resistance 18.8 |     |      |     |      |

| θJb    | Junction to Base thermal resistance    |                                        |     | 0.62 |     |      |

| θJA0   | Junction to ambient thermal resistance | flow = 0 m/s                           |     | 36.1 |     | °C/W |

| θJA1   | Junction to ambient thermal resistance | flow = 1 m/s                           |     | 31.4 |     |      |

| θJA2   | Junction to ambient thermal resistance | flow = $2 \text{ m/s}$                 |     | 30.2 |     |      |

## **Electrical Characteristics (Power Supply)**

Unless otherwise specified: Vcc =  $3.3V/2.5V \pm 5\%$ , Vcco =  $3.3V/2.5V \pm 5\%$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , CLKin driven differentially, input slew rate  $\ge 3V/ns$ . Typical values represent most likely parametric norms at Vcc= $3.3V/Cco=3.3V/T_A=25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not ensured.<sup>[1]</sup>

| Symbol                                 | Description                       | Test Conditions             | MIN   | TYP | MAX   | Unit |

|----------------------------------------|-----------------------------------|-----------------------------|-------|-----|-------|------|

| Power Sup                              | oly                               |                             |       |     |       |      |

|                                        |                                   | 3.3V                        | 3.135 | 3.3 | 3.465 |      |

| Vcc                                    | Core Supply Voltage               | 2.5V                        | 2.375 | 2.5 | 2.625 | V    |

| V <sub>CCOA</sub><br>V <sub>CCOB</sub> | Output Supply                     | 3.3V                        | 3.135 | 3.3 | 3.465 | V    |

| Vccoc                                  | Voltage Range <sup>[1]</sup>      | 2.5V                        | 2.375 | 2.5 | 2.625 | v    |

| Current Con                            | sumption                          |                             |       |     |       |      |

| I <sub>CC_CORE</sub>                   | Core Supply Current.              |                             |       | 50  | 100   | mA   |

| ICCO_PECL                              | Output Supply Current<br>(LVPECL) | All LVPECL outputs unloaded |       | 60  | 100   | mA   |

| ICCO_LVDS                              | Output Supply Current<br>(LVDS)   | All LVDS outputs loaded     |       | 50  | 90    | mA   |

| ICCO_HCSL                              | Output Supply Current<br>(HCSL)   | All HCSL outputs unloaded   |       | 35  | 80    | mA   |

| Temperatur                             | e                                 |                             |       |     |       |      |

| T <sub>A</sub>                         | Ambient Temperature<br>Range      |                             | -40   | 25  | 125   | °C   |

| Тв                                     | PCB operating Temperature         |                             | -40   |     | 125   | °C   |

Note

<sup>[1]</sup> The output supply voltages or pins ( $V_{CCOB}$ ,  $V_{CCOB}$ , and  $V_{CCOC}$ ) will be called  $V_{CCO}$  in general when no distinction is needed, or when the output supply can be inferred from the output bank/type.

### **Electrical Characteristics (Inputs)**

Unless otherwise specified: Vcc =  $3.3V/2.5V \pm 5\%$ , Vcco =  $3.3V/2.5V \pm 5\%$ ,  $-40^{\circ}C \le T_{A} \le 125^{\circ}C$ , CLKin driven differentially, input slew rate  $\ge 3V/ns$ . Typical values represent most likely parametric norms at Vcc= $3.3V/Cco=3.3V/T_{A}=25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not ensured.<sup>[1]</sup>

| Symbol             | Description                               | Test Conditions                                             | MIN  | ТҮР | MAX     | Unit |

|--------------------|-------------------------------------------|-------------------------------------------------------------|------|-----|---------|------|

| CMOS CONT          | ROL INPUTS (CLKin_SELn ,                  | CLKout_TYPEn , REFout_EN)                                   |      |     |         |      |

| Vін                | High-Level Input Voltage                  | VCC=3.3V                                                    | 1.6  |     | Vcc     | V    |

| VIN                | Thigh Level input voltage                 | VCC=2.5V                                                    | 1.2  |     | Vcc     | V    |

| V <sub>IL</sub>    | Low-Level Input Voltage                   | VCC=3.3V                                                    | GND  |     | 0.4     | V    |

|                    |                                           | VCC=2.5V                                                    | GND  |     | 0.4     |      |

| I <sub>Н</sub>     | High-Level Input Current                  | $V_{IH} = Vcc$ , Internal pull down                         |      | 0.4 | 50      | μA   |

|                    | Low-Level Input Current                   | $V_{IL} = 0 V$ , Internal pull down                         | -5   | 0.1 |         | μA   |

|                    | JTS (CLKin0/CLKin0*, CLKin                |                                                             |      |     |         |      |

| IIH                | Input High current                        | Input =V <sub>CC</sub>                                      |      |     | 150     | μA   |

| Ι <sub>ΙL</sub>    | Input Low current                         | Input = GND                                                 | -150 |     |         | μA   |

| C <sub>IN</sub>    | Differential<br>Input capacitance         |                                                             |      | 3   |         | pF   |

| VIHD               | Differential Input High<br>Voltage        |                                                             |      |     | Vcc+0.3 | V    |

| V <sub>ILD</sub>   | Differential Input Low<br>Voltage         | CLKin driven differentially                                 | -0.3 |     |         | V    |

| Vid                | Differential Input Voltage<br>Swing       |                                                             | 0.15 |     | 1.3     | V    |

|                    | <b>5</b> ///                              | V <sub>ID</sub> = 150mV                                     | 0.25 |     | Vcc-1.2 | V    |

| V <sub>CMD</sub>   | Differential Input Common<br>Mode Voltage | V <sub>ID</sub> = 350mV                                     | 0.25 |     | Vcc-1.1 | V    |

|                    | wode voltage                              | V <sub>ID</sub> = 800mV                                     | 0.25 |     | Vcc-0.9 | V    |

| ISO <sub>MUX</sub> | Mux Isolation, CLKin 0 to<br>CLKin1       | f <sub>OFFSET</sub> > 50kHz,<br>P <sub>CLKin</sub> x = 0dBm |      | -89 |         | dBc  |

| VIH                | Single-Ended Input High                   | VCC=3.3V                                                    | 2.0  |     | Vcc+0.3 | V    |

| VIH                | Voltage                                   | VCC=2.5V                                                    | 1.7  |     | Vcc+0.3 | V    |

| VIL                | Single-Ended Input Low                    | VCC=3.3V                                                    | -0.3 |     | 0.8     | V    |

|                    | Voltage                                   | VCC=2.5V                                                    | -0.3 |     | 0.7     | V    |

| CRYSTAL IN         | ITERFACE (OSCin, OSCout)                  |                                                             |      |     |         |      |

| Fclk               | External Clock<br>Frequency Range         | OSCin driven single-ended,<br>OSCout floating               |      |     | 250     | MHz  |

| Fxtal              | Crystal Frequency Range                   | Fundamental mode                                            | 10   |     | 50      | MHz  |

| ESR                | Equivalent Series<br>Resistance (ESR)     |                                                             |      |     | 70      | Ω    |

| Cs                 | Shunt Capacitance                         |                                                             |      |     | 7       | pF   |

| $C_{L}$            | Load Capacitance                          |                                                             | 10   |     | 18      | pF   |

| Pd                 | Drive Level                               |                                                             |      |     | 500     | μW   |

Note

[1] The output supply voltages or pins ( $V_{CCOA}$ ,  $V_{CCOB}$ , and  $V_{CCOC}$ ) will be called  $V_{CCO}$  in general when no distinction is needed, or when the output supply can be inferred from the output bank/type.

## **Electrical Characteristics (LVPECL)**

Unless otherwise specified: Vcc =  $3.3V/2.5V \pm 5\%$ , Vcco =  $3.3V/2.5V \pm 5\%$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , CLKin driven differentially, input slew rate  $\ge 3V/ns$ . Typical values represent most likely parametric norms at Vcc= $3.3V/Cco=3.3V,T_A=25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not ensured.<sup>[1]</sup>

| Symbol                | Description                               | Test Conditions                                                                  | MIN                   | TYP  | MAX                   | Unit   |

|-----------------------|-------------------------------------------|----------------------------------------------------------------------------------|-----------------------|------|-----------------------|--------|

| LVPECL OU             | TPUTS (CLKoutAn/0                         | CLKoutAn*, CLKoutBn/CLKoutBn*)                                                   |                       |      |                       |        |

| f <sub>CLKout</sub>   | Maximum Output<br>Frequency               | $V_{OD} \ge 400 \text{mV}, \text{ R}_{L} = 100 \Omega \text{ differential}$      |                       | 1.5  |                       | GHz    |

| Jitter <sub>ADD</sub> |                                           | CLKin: 156.25MHz, Slew rate $\geq$ 3V/ns, 10 kHz to 20MHz                        |                       | 20   |                       | fs     |

| Silleradd             | Jitter                                    | CLKin: 156.25MHz, Slew rate $\ge$ 3V/ns, 1MHz to 20MHz                           |                       | 10   |                       | fs     |

| Ps                    | Phase noise<br>f <sub>offset</sub> ≥10MHz | CLKin: 156.25MHz,<br>Slew rate $\geq$ 3V/ns                                      |                       | -156 |                       | dBc/Hz |

| t <sub>R</sub>        | Output Rise Time 20% to 80%               | $R_T = 150\Omega$ to GND, $R_L = 100\Omega$ differential                         | 120                   | 150  | 300                   | ps     |

| t⊧                    | Output Fall Time 80% to 20%               | CL ≤ 5pF                                                                         | 120                   | 150  | 300                   | ps     |

| tpd_pecl              | Propagation<br>Delay CLKin-to-<br>LVPECL  | $R_T$ = 150 $\Omega$ to GND, $R_L$ = 100 $\Omega$ differential, $C_L \leq 5 p F$ |                       | 500  |                       | ps     |

| tsk(O)                | Output Skew<br>LVPECL                     | Skew specified between any two CLKouts                                           |                       | 30   | 50                    | ps     |

| $t_{SK(P)}^{[2]}$     | Part to Part Skew                         | with the same buffer type.                                                       |                       | 80   | 120                   | ps     |

|                       |                                           | Frequency< 650MHz                                                                | 48%                   |      | 52%                   |        |

| TODC                  | Duty Cycle                                | Frequency< 1GHz                                                                  | 45%                   |      | 55%                   |        |

|                       |                                           | Frequency< 1.5GHz                                                                | 40%                   |      | 60%                   |        |

| V <sub>OH</sub>       | Output High<br>Voltage                    | TA = 25°C, DC Measurement,                                                       | V <sub>CCO</sub> -1.4 |      | V <sub>CCO</sub> -0.9 | V      |

| Vol                   | Output Low<br>Voltage                     | $R_T = 50\Omega$ to Vcco - 2 V                                                   | Vcco - 2.2            |      | Vcco-1.7              | V      |

|                       | Output Voltage                            | Frequency< 1GHz                                                                  | 500                   |      | 1100                  | mV     |

| Vod                   | Swing Single-<br>ended                    | Frequency≥ 1GHz                                                                  | 400                   |      | 1000                  | mV     |

Note

[1] The output supply voltages or pins ( $V_{CCOB}$ ,  $V_{CCOB}$ , and  $V_{CCOC}$ ) will be called  $V_{CCO}$  in general when no distinction is needed, or when the output supply can be inferred from the output bank/type.

[2] This parameter is guaranteed by design.

### **Electrical Characteristics (LVDS)**

Unless otherwise specified: Vcc =  $3.3V/2.5V \pm 5\%$ , Vcco =  $3.3V/2.5V \pm 5\%$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , CLKin driven differentially, input slew rate  $\ge 3V/ns$ . Typical values represent most likely parametric norms at Vcc= $3.3V/Cco=3.3V,T_A=25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not ensured.<sup>[1]</sup>

| Symbol                                     | Description                                            | Test Conditions                                                                     | MIN | ТҮР  | MAX | Unit   |

|--------------------------------------------|--------------------------------------------------------|-------------------------------------------------------------------------------------|-----|------|-----|--------|

| LVDS OUTP                                  | PUTS (CLKoutAn/CLKou                                   | tAn*, CLKoutBn/CLKoutBn*)                                                           |     |      |     |        |

| f <sub>CLKout</sub>                        | Maximum Output<br>Frequency                            | $V_{OD} \ge 400 \text{mV}, \text{ R}_{L} = 100 \Omega$ differential                 |     | 1.5  |     | GHz    |

| littor                                     |                                                        | CLKin: 156.25MHz, Slew rate $\geq$ 3V/ns, 10kHz to 20MHz                            |     | 20   |     | fs     |

| Jitter <sub>ADD</sub> Additive RMS JitterR | CLKin: 156.25MHz, Slew rate $\ge$ 3V/ns, 1MHz to 20MHz |                                                                                     | 10  |      | fs  |        |

| Ps                                         | Phase noise<br>f <sub>offset</sub> ≥10MHz              | CLKin: 156.25MHz,<br>Slew rate $\geq$ 3V/ns                                         |     | -156 |     | dBc/Hz |

| t <sub>R</sub>                             | Output Rise Time 20% to 80%                            | $R_L$ = 100Ω differential, CL ≤ 5pF                                                 | 120 | 150  | 300 | ps     |

| t⊧                                         | Output Fall Time 80% to 20%                            |                                                                                     | 120 | 150  | 300 | ps     |

| tpd_lvds                                   | Propagation Delay<br>CLKin-to LVDS                     | $R_L$ = 100 $\Omega$ differential, $C_L \le 5pF$                                    |     | 500  |     | ps     |

| tsk(0)                                     | Output Skew LVDS                                       | Skew specified between any two                                                      |     | 15   | 40  | ps     |

| t <sub>SK(PP)</sub> [2]                    | Part-to-Part Output<br>Skew LVDS                       | CLKouts with the same buffer type.<br>$R_L = 100\Omega$ differential, $C_L \le 5pF$ |     | 80   | 120 | ps     |

|                                            |                                                        | Frequency< 650MHz                                                                   | 47% |      | 53% |        |

| TODC                                       | Duty Cycle                                             | Frequency< 1GHz                                                                     | 45% |      | 55% |        |

|                                            |                                                        | Frequency< 1.5GHz                                                                   | 40% |      | 60% |        |

| Vон                                        | Output High Voltage                                    |                                                                                     |     | 1.45 |     | V      |

| Vol                                        | Output Low Voltage                                     |                                                                                     |     | 1.05 |     | V      |

| Vos                                        | Output Offset Voltage                                  | T 0500 DO M                                                                         |     | 1.25 |     | V      |

| $\Delta  V_{OS}$                           | Change in Vos for<br>Complementary<br>Output States    | $T_A = 25^{\circ}C$ , DC Measurement,<br>R <sub>L</sub> = 100 $\Omega$ differential |     |      | 50  | mV     |

|                                            |                                                        | Frequency< 1GHz                                                                     | 300 |      | 500 | mV     |

| Vod                                        | Output Voltage Swing                                   | Frequency≥ 1GHz                                                                     | 250 |      | 450 | mV     |

Note

[1] The output supply voltages or pins ( $V_{CCOB}$ ,  $V_{CCOB}$ , and  $V_{CCOC}$ ) will be called  $V_{CCO}$  in general when no distinction is needed, or when the output supply can be inferred from the output bank/type.

[2] This parameter is guaranteed by design.

### **Electrical Characteristics (HSCL)**

Unless otherwise specified: Vcc =  $3.3V/2.5V \pm 5\%$ , Vcco =  $3.3V/2.5V \pm 5\%$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , CLKin driven differentially, input slew rate  $\ge 3V/ns$ . Typical values represent most likely parametric norms at Vcc= $3.3V/Cco=3.3V/T_A=25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not ensured.<sup>[1]</sup>

| Symbol                                        | Description                                                    | Test Conditions                                                                         | MIN  | TYP  | MAX | Unit     |  |  |  |

|-----------------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------|------|------|-----|----------|--|--|--|

| HSCL (CLKoutAn/CLKoutAn*, CLKoutBn/CLKoutBn*) |                                                                |                                                                                         |      |      |     |          |  |  |  |

| f <sub>CLKout</sub>                           | Output FrequencyRange                                          | $C_L \leqslant 5 pF$                                                                    |      |      | 250 | MHz      |  |  |  |

| Jitteradd_pcie-<br>CC                         | Additive PCIe Phase Jitter<br>(Common Clocked<br>Architecture) | PCIe Gen2 Hi Band (5.0 GT/s)                                                            |      | 110  | 310 | fs (RMS) |  |  |  |

|                                               |                                                                | PCIe Gen2 Lo Band (5.0 GT/s)                                                            |      | 10   | 20  |          |  |  |  |

|                                               |                                                                | PCIe Gen3 (8.0 GT/s)                                                                    |      | 35   | 60  |          |  |  |  |

|                                               |                                                                | PCIe Gen4 (16.0 GT/s) [3] [4]                                                           |      | 30   | 60  |          |  |  |  |

|                                               |                                                                | PCIe Gen5 (32.0 GT/s) [3] [5]                                                           |      | 15   | 25  |          |  |  |  |

|                                               |                                                                | PCIe Gen2 (5.0 GT/s)                                                                    |      | 80   | 300 | fs (RMS) |  |  |  |

| Jitteradd_PCle-<br>IR                         | Additive PCIe Phase Jitter                                     | PCIe Gen3 (8.0 GT/s)                                                                    |      | 50   | 150 |          |  |  |  |

|                                               | (IR Architectures - SRIS,<br>SRNS)                             | PCle Gen4 (16.0 GT/s) <sup>[3][4]</sup>                                                 |      | 40   | 150 |          |  |  |  |

|                                               |                                                                | PCIe Gen5 (32.0 GT/s) <sup>[3] [5]</sup>                                                |      | 25   | 60  |          |  |  |  |

| Jitter <sub>ADD</sub>                         | Additive RMS Jitter                                            | CLKin: 156.25MHz, Slew rate ≥ 3V/ns, 10kHz to 20MHz                                     |      | 20   |     | fs       |  |  |  |

|                                               |                                                                | CLKin: 156.25MHz, Slew rate $\geq$ 3V/ns, 1MHz to 20MHz                                 |      | 10   |     | fs       |  |  |  |

| Ps                                            | Phase noise<br>f <sub>offset</sub> ≥10MHz                      | CLKin: 156.25MHz,<br>Slew rate $\ge$ 3V/ns                                              |      | -156 |     | dBc/Hz   |  |  |  |

| t <sub>R</sub>                                | Output Rise Time 20% to 80%                                    | 250MHz, $R_L$ = 50 $\Omega$ to GND, $C_L \leq$                                          | 300  |      | 700 | ps       |  |  |  |

| t <sub>F</sub>                                | Output Fall Time 80% to 20%                                    | 5pF                                                                                     | 300  |      | 700 | ps       |  |  |  |

| tPD_HSCL                                      | Propagation Delay CLKin-to<br>HSCL                             | 100MHz                                                                                  |      | 900  |     | ps       |  |  |  |

| t <sub>SK(O)</sub>                            | Output Skew                                                    | Skew specified between any two<br>CLKouts with the same buffer type.<br>Load conditions |      | 15   | 40  | ps       |  |  |  |

| t <sub>SK(PP)</sub> [2]                       | Part-to-Part Output Skew                                       |                                                                                         |      | 80   | 120 | ps       |  |  |  |

| T <sub>ODC</sub>                              | Duty Cycle                                                     | Frequency< 250MHz                                                                       | 48%  |      | 52% |          |  |  |  |

| Maria                                         | Output High Voltage                                            | $R_T = 50\Omega$ to GND, V <sub>CCO</sub> =2.5V                                         | 500  |      | 900 | mV       |  |  |  |

| V <sub>OH</sub>                               |                                                                | $R_T = 50\Omega$ to GND, Vcco=3.3V                                                      | 700  | 800  | 900 | mV       |  |  |  |

| V <sub>OL</sub>                               | Output Low Voltage                                             | $T_A = 25^{\circ}C$ , DC Measurement, $R_T = 50\Omega$ to GND                           | -150 |      | 150 | mV       |  |  |  |

| V <sub>CROSS</sub>                            | Absolute Crossing Voltage                                      | R <sub>L</sub> = 50Ω to GND, C <sub>L</sub> $\leq$ 5pF                                  |      | 460  |     | mV       |  |  |  |

| $\Delta$ Vcross                               | Total Variation of VcRoss                                      |                                                                                         |      |      | 140 | mV       |  |  |  |

Note

[2] This parameter is guaranteed by design.

[5] Note that 0.25ps RMS is to be used in channel simulations to account for additional noise in a real system.

<sup>[1]</sup> The output supply voltages or pins ( $V_{CCOB}$ ,  $V_{CCOB}$ , and  $V_{CCOC}$ ) will be called  $V_{CCO}$  in general when no distinction is needed, or when the output supply can be inferred from the output bank/type.

<sup>[3]</sup> SSC spurs from the fundamental and harmonics are removed up to a cutoff frequency of 2MHz taking care to minimize removal of any non-SSC content.

<sup>[4]</sup> Note that 0.7ps RMS is to be used in channel simulations to account for additional noise in a real system.

## **Electrical Characteristics (LVCMOS)**

Unless otherwise specified: Vcc =  $3.3V/2.5V \pm 5\%$ , Vcco =  $3.3V/2.5V \pm 5\%$ ,  $-40^{\circ}C \le T_A \le 125^{\circ}C$ , CLKin driven differentially, input slew rate  $\ge 3V/ns$ . Typical values represent most likely parametric norms at Vcc= $3.3V/Cco=3.3V/T_A=25^{\circ}C$ , and at the Recommended Operation Conditions at the time of product characterization and are not ensured.<sup>[1]</sup>

| Symbol                 | Description                               | Test Conditions                                       | MIN | TYP  | MAX | Unit   |  |  |

|------------------------|-------------------------------------------|-------------------------------------------------------|-----|------|-----|--------|--|--|

| LVCMOS OUTPUT (REFout) |                                           |                                                       |     |      |     |        |  |  |

| f <sub>CLKout</sub>    | Output Frequency<br>Range                 | Crystal Input                                         | 10  |      | 50  | MHz    |  |  |

|                        |                                           | Single Ended input                                    |     |      | 250 | MHz    |  |  |

| Jitter <sub>ADD</sub>  | additive jitter RMS                       | Crystal Input                                         |     | 300  |     | fs     |  |  |

|                        |                                           | Single Ended input                                    |     | 30   |     | fs     |  |  |

| Ps                     | Phase noise<br>f <sub>offset</sub> ≥10MHz | CLKin: 156.25MHz, Slew rate $\ge$ 3V/ns               |     | -156 |     | dBc/Hz |  |  |

| t <sub>R</sub>         | Output Rise Time 20% to 80%               | inches with 500 characteristic                        |     | 225  | 400 | ps     |  |  |

| t⊨                     | Output Fall Time 80% to 20%               |                                                       |     | 225  | 400 | ps     |  |  |

| tpd cmos               | Propagation Delay<br>CLKin-to-LVCMOS      | Vcco = 3.3V, 25MHz                                    |     | 2200 |     | ps     |  |  |

| PD_CMOS                |                                           | V <sub>CCO</sub> = 2.5V, 25MHz                        |     | 2200 |     | ps     |  |  |

| t <sub>EN</sub>        | Output Enable Time                        |                                                       | 2   |      | 4   | cycles |  |  |

| t <sub>DIS</sub>       | Output Disable Time                       |                                                       | 2   |      | 4   | cycles |  |  |

| TODC                   | Duty Cycle                                | 50% input clock duty cycle; CL=10pF                   | 45% |      | 55% |        |  |  |

|                        | Output High Voltage                       | V <sub>CCO</sub> =3.3V +/-5%, I <sub>OH</sub> = 8mA   | 2.3 |      |     | V      |  |  |

| N                      |                                           | V <sub>CCO</sub> =2.5V +/-5%, I <sub>OH</sub> = 8mA   | 1.5 |      |     | V      |  |  |

| Vон                    |                                           | Vcco =3.3V +/-5%, Iон = 24mA                          | 2.1 |      |     | V      |  |  |

|                        |                                           | Vcco =2.5V +/-5%, Iон = 16mA                          | 1.5 |      |     | V      |  |  |

|                        | Output Low Voltage                        | V <sub>CCO</sub> =3.3V +/-5%, I <sub>OL</sub> = -8mA  |     |      | 0.5 | V      |  |  |

| V <sub>OL</sub>        |                                           | V <sub>CCO</sub> =2.5V +/-5%, I <sub>OL</sub> = -8mA  |     |      | 0.4 | V      |  |  |

|                        |                                           | V <sub>CCO</sub> =3.3V +/-5%, I <sub>OL</sub> = -24mA |     |      | 1   | V      |  |  |

|                        |                                           | V <sub>CCO</sub> =2.5V +/-5%, I <sub>OL</sub> = -16mA |     |      | 0.8 | V      |  |  |

| Ro lvcmos              | Output Impedance                          | Vcco =3.3V +/-5%,                                     |     | 17   |     | Ω      |  |  |

| INO_LVUMOS             |                                           | V <sub>CCO</sub> =2.5V +/-5%,                         |     | 22   |     | Ω      |  |  |

Note

[1] The output supply voltages or pins (V<sub>CCOB</sub>, V<sub>CCOB</sub>, and V<sub>CCOC</sub>) will be called V<sub>CCO</sub> in general when no distinction is needed, or when the output supply can be inferred from the output bank/type.

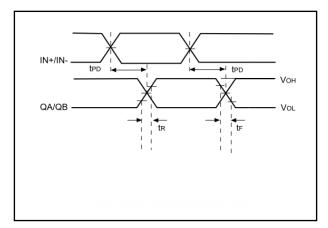

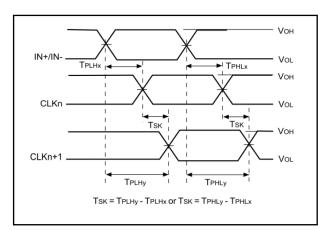

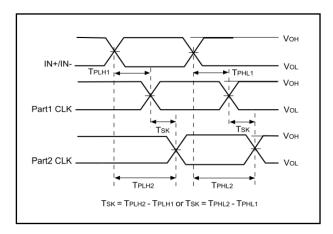

### **Figure of Timing Characteristics**

Unless otherwise specified: Vcc = 3.3V, Vcco = 3.3V, T<sub>A</sub> = 25°C, CLKin driven differentially, input slew rate  $\geq$  3V/ns.

**Propagation Delay**

Output Skew

#### Part to Part Skew

### **Figure of Timing Characteristics**

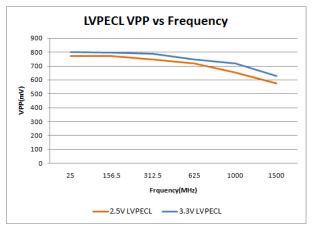

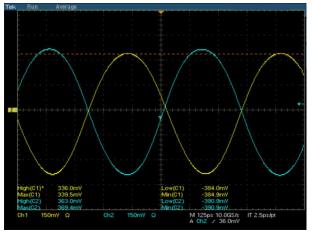

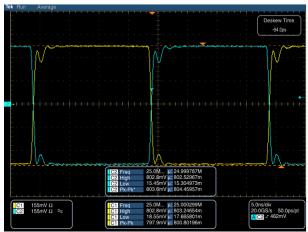

Unless otherwise specified: Vcc = 3.3V, Vcco = 3.3V, T<sub>A</sub> = 25°C, CLKin driven differentially, input slew rate  $\geq$  3V/ns.

#### LVPECL Output Swing vs. Frequency

#### LVPECL Output Swing at 1.5GHz

HSCL Output Swing at 25MHz

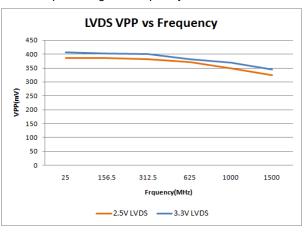

LVDS Output Swing vs. Frequency

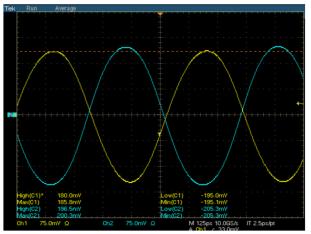

LVDS Output Swing at 1.5GHz

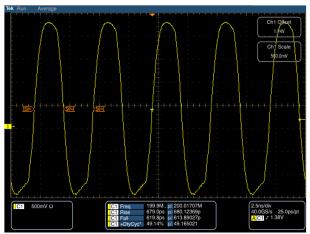

LVCMOS Output Swing at 200MHz

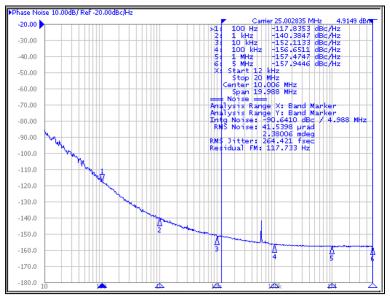

## **Figure of Timing Characteristics**

Unless otherwise specified: Vcc = 3.3V, Vcco = 3.3V, T<sub>A</sub> = 25°C, CLKin driven differentially, input slew rate  $\ge$  3V/ns.

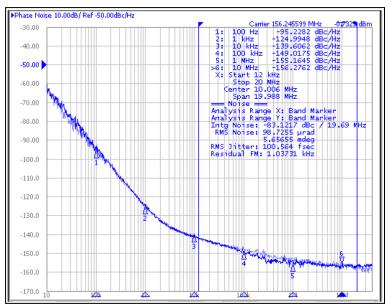

Output phase noise (Dark Blue) vs Input Phase noise (light blue)

Additive jitter is calculated at 156.25MHz~27fs RMS (12kHz to 20MHz).

Additive jitter = (Output jitter<sup>2</sup> - Input jitter<sup>2</sup>)<sup>1/2</sup>

Total Phase Jitter with 25MHz XTAL ~ 264fs RMS (12kHz ~20MHz)

### **Feature Description**

#### VCC and VCCO Power Supplies

The RS00304Q has separate 3.3V/2.5V core supply (V<sub>CC</sub>) and 3 independent 3.3V/2.5V output power supplies (V<sub>CCOA</sub>, V<sub>CCOB</sub>, V<sub>CCOC</sub>). Output supply operation at 2.5V enables lower power consumption and output-level compatibility with 2.5V receiver devices. The output levels for LVPECL (V<sub>OH</sub>, V<sub>OL</sub>) and LVCMOS (V<sub>OH</sub>) are referenced to its respective Vcco supply, while the output levels for LVDS and HCSL are relatively constant over the specified Vcco range.

#### **Clock Inputs**

The input clock can be selected from CLKin0/CLKin0\*, CLKin1/CLKin1\*, or OSCin. Clock input selection is controlled using the CLKin\_SEL[1:0] inputs. When CLKin0 or CLKin1 is selected, the crystal circuit is powered down. When OSCin is selected, the crystal oscillator circuit will start-up and its clock will be distributed to all outputs. Alternatively, OSCin may be driven by a single-ended clock (up to 250MHz) instead of a crystal.

When OSCin is selected, the output state will be an inverted copy of the OSCin input state.

#### **Clock Outputs**

The differential output buffer type for both Bank A and B outputs are configured using the CLKout\_TYPE[1:0]. For applications where all differential outputs are not needed, any unused output pin should be left floating with a minimum copper length (see note below) to minimize capacitance and potential coupling and reduce power consumption. If all differential outputs are not used, it is recommended to disable (Hi-Z) the banks to reduce power.

For best soldering practices, the minimum trace length for any unused pin should extend to include the pin solder mask. This way during reflow, the solder has the same copper area as connected pins. This allows for good, uniform fillet solder joints helping to keep the IC level during reflow.

#### **Reference Output**

The reference output (REFout) provides a LVCMOS copy of the selected input clock. The LVCMOS output high level is referenced to the Vcco voltage. REFout can be enabled or disabled using the enable input pin, REFout\_EN.

The REFout\_EN input is internally synchronized with the selected input clock by the SYNC block. This synchronizing function prevents glitches and runt pulses from occurring on the REFout clock when enabled or disabled. REFout will be enabled within 4 cycles ( $t_{EN}$ ) of the input clock after REFout\_EN is toggled high. REFout will be disabled within 4 cycles ( $t_{DIS}$ ) of the input clock after REFout\_EN is toggled low.

When REFout is disabled, the use of a resistive loading can be used to set the output to a predetermined level. For example, if REFout is configured with a  $1k\Omega$  load to ground, then the output will be pulled to low when disabled.

### **Application Information**

#### **Driving the Clock Inputs**

The RS00304Q has two universal inputs (CLKin0/CLKin0\* and CLKin1/CLKin1\*) that can accept DC-coupled 3.3V/2.5V LVPECL, LVDS, CML, SSTL, and other differential and single-ended signals that meet the input requirements specified in *Electrical Characteristics*. The device can accept a wide range of signals due to its wide input common mode voltage range and input voltage swing ( $V_{ID}$ ) / dynamic range. For 50% duty cycle and DC-balanced signals, AC coupling may also be employed to shift the input signal to within the range.

To achieve the best possible phase noise and jitter performance, it is mandatory for the input to have high slew rate of 3V/ns (differential) or higher. Driving the input with a lower slew rate will degrade the noise floor and jitter. For this reason, a differential signal input is recommended over single-ended because it typically provides higher slew rate and common-mode-rejection.

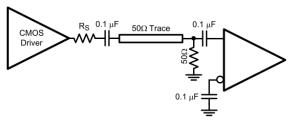

While it is recommended to drive the CLKin/CLKin\* pair with a differential signal input, it is possible to drive it with a single-ended clock provided it conforms to the Single-Ended Input specifications for CLKin pins listed in the Electrical Characteristics. For large single-ended input signals, such as 3.3V or 2.5V LVCMOS, a 50 $\Omega$  load resistor should be placed near the input for signal attenuation to prevent input overdrive as well as for line termination to minimize reflections. Again, the single-ended input slew rate should be as high as possible to minimize performance degradation.

The CLKin input has an internal bias voltage of about 1.4V, so the input can be AC coupled. The output impedance of the LVCMOS driver plus Rs should be close to  $50\Omega$  to match the characteristic impedance of the transmission line and load termination.

Single-Ended LVCMOS Input, AC Coupling

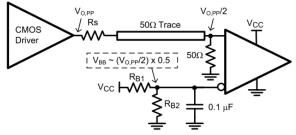

A single ended clock may also be DC coupled to CLKinX. A  $50\Omega$  load resistor should be placed near the CLKin input for signal attenuation and line termination. Because half of the single-ended swing of the driver (V<sub>0,PP</sub> / 2) drives CLKinX, CLKinX\* should be externally biased to the midpoint voltage of the attenuated input swing ((V<sub>0,PP</sub> / 2) × 0.5). The external bias voltage should be within the specified input common voltage range. This can be achieved using external biasing resistors in the k $\Omega$  range (R<sub>B1</sub> and R<sub>B2</sub>) or another low-noise voltage reference. This will ensure the input swing crosses the threshold voltage at a point where the input slew rate is the highest.

If the LVCMOS driver cannot achieve sufficient swing with a DC-terminated 50 $\Omega$  load at the CLKinX input, then consider connecting the 50 $\Omega$  load termination to ground through a capacitor (C<sub>AC</sub>). This AC termination blocks the DC load current on the driver, so the voltage swing at the input is determined by the voltage divider formed by the source (Ro + Rs) and 50 $\Omega$  load resistors. The value for C<sub>AC</sub> depends on the trace delay, Td, of the 50 $\Omega$  transmission line, where C<sub>AC</sub>>= 3\*Td/50 $\Omega$ .

Single-Ended LVCMOS Input, DC Coupling with Common Mode Biasing

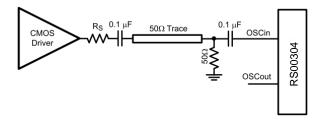

If the crystal oscillator circuit is not used, it is possible to drive the OSCin input with a single-ended external clock. The input clock should be AC coupled to the OSCin pin, which has an internally- generated input bias voltage, and the OSCout pin should be left floating. While OSCin provides an alternative input to multiplex an external clock, it is recommended to use either universal input (CLKinX) since it offers higher operating frequency, better common mode and power supply noise rejection, and greater performance over supply voltage and temperature variations.

Driving OSCin with a Single-Ended Input

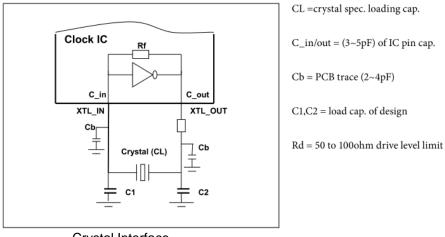

### **Crystal Interface**

The RS00304Q has an integrated crystal oscillator circuit that supports a fundamental mode, AT-cut crystal. The crystal interface is shown in bellow figure.

Crystal Interface

Design guide:  $C1=C2=2*C_{L} - (Cb + C_in/out)$  to meet the target accuracy.(in +/- 20ppm) Example 1: Select C<sub>L</sub>=18pF crystal, C1=C2=2\*(18pF) - (4pF+5pF)=27pF, check the datasheet of crystal.

Example 2: For higher frequency crystal ( $\geq$ 20MHz), can use the formula C1=C2=2\*(CL-6), it can do fine tune of C1, C2 for more accurate ppm if necessary.

## Termination and Use of Clock Drivers

When terminating clock drivers keep in mind these guidelines for optimum phase noise and jitter performance:

- Transmission line theory should be followed for good impedance matching to prevent reflections.

- · Clock drivers should be presented with the proper loads.

- LVDS outputs are current drivers and require a closed current loop.

- HCSL drivers are switched current outputs and require a DC path to ground via  $50\Omega$  termination.

- LVPECL outputs are open emitter and require a DC path to ground.

- Receivers should be presented with a signal biased to their specified DC bias level (common mode voltage) for

proper operation. Some receivers have self-biasing inputs that automatically bias to the proper voltage level; in

this case, the signal should normally be AC coupled.

It is possible to drive a non-LVPECL or non-LVDS receiver with a LVDS or LVPECL driver as long as the above guidelines are followed. Check the data sheet of the receiver or input being driven to determine the best termination and coupling method to be sure the receiver is biased at the optimum DC voltage (common mode voltage).

### Termination for DC-Coupled Differential Operation

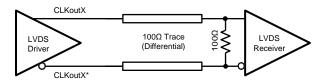

For DC-coupled operation of an LVDS driver, terminate with  $100\Omega$  as close as possible to the LVDS receiver as shown in the figure.

Differential LVDS Operation, DC Coupling, No Biasing by the Receiver

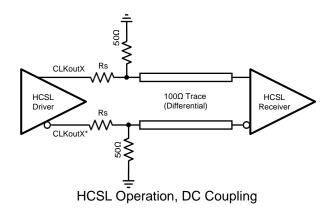

For DC-coupled operation of an HCSL driver, terminate with  $50\Omega$  to ground near the driver output. Series resistors, Rs, may be used to limit overshoot due to the fast transient current. Because HCSL drivers require a DC path to ground, AC coupling is not allowed between the output drivers and the  $50\Omega$  termination resistors.

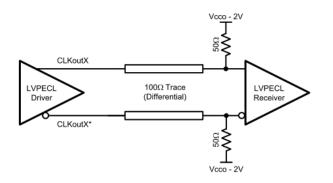

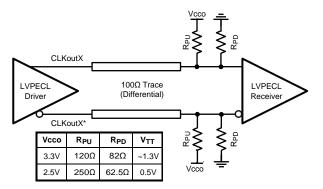

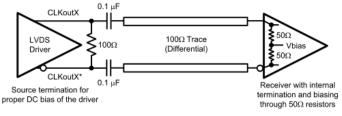

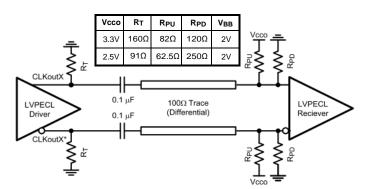

For DC-coupled operation of an LVPECL driver, terminate with  $50\Omega$  to Vcco - 2V. Alternatively terminate with a Thevenin equivalent circuit for Vcco (output driver supply voltage) = 3.3V and 2.5V. In the Thevenin equivalent circuit, the resistor dividers set the output termination voltage (V<sub>TT</sub>) to Vcco - 2V.

Differential LVPECL Operation, DC Coupling

Differential LVPECL Operation, DC Coupling, Thevenin Equivalent

### Termination for AC-Coupled Differential Operation

AC coupling allows for shifting the DC bias level (common mode voltage) when driving different receiver standards. Because AC coupling prevents the driver from providing a DC bias voltage at the receiver, it is important to ensure the receiver is biased to its ideal DC level.

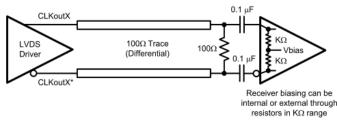

When driving differential receivers with an LVDS driver, the signal may be AC coupled by adding DC-blocking capacitors; however the proper DC bias point needs to be established at both the driver side and the receiver side. The recommended termination scheme depends on whether the differential receiver has integrated termination resistors or not.

When driving a differential receiver without internal  $100\Omega$  differential termination, the AC-coupling capacitors should be placed between the load termination resistor and the receiver to allow a DC path for proper biasing of the LVDS driver. The load termination resistor and AC-coupling capacitors should be placed as close as possible to the receiver inputs to minimize stub length. The receiver can be biased internally or externally to a reference voltage within the receiver's common mode input range through resistors in the kilo-ohm range.

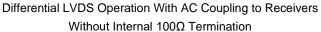

When driving a differential receiver with internal  $100\Omega$  differential termination, a source termination resistor should be placed before the AC-coupling capacitors for proper DC biasing of the driver. However, with a  $100\Omega$  resistor at the source and the load (that is, double terminated), the equivalent resistance seen by the LVDS driver is  $50\Omega$ which causes the effective signal swing at the input to be reduced by half. If a self-terminated receiver requires input swing greater than 250mVpp (differential) as well as AC coupling to its inputs, then the LVDS driver with the double-terminated arrangement may not meet the minimum input swing requirement; alternatively, the LVPECL or HCSL output driver format with AC coupling is recommended to meet the minimum input swing required by the self-terminated receiver.

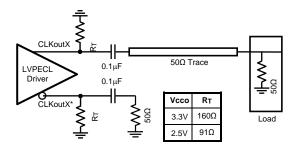

When using AC coupling with LVDS outputs, there may be a startup delay observed in the clock output due to capacitor charging. The examples in bellow figure use 0.1µF capacitors, but this value may be adjusted to meet the startup requirements for the particular application.

Differential LVDS Operation With AC Coupling to Receivers With Internal 100Ω Termination

LVPECL drivers require a DC path to ground. When AC coupling an LVPECL signal use  $160\Omega$  emitter resistors (or  $91\Omega$  for Vcco = 2.5V) close to the LVPECL driver to provide a DC path to ground. For proper receiver operation, the signal should be biased to the DC bias level (common mode voltage) specified by the receiver. The typical DC bias voltage (common mode voltage) for LVPECL receivers is 2V. Alternatively, a Thevenin equivalent circuit forms a valid termination for Vcco = 3.3V and 2.5V.

Differential LVPECL Operation, AC Coupling, Thevenin Equivalent

### Termination for Single-Ended Operation

A balun can be used with either LVDS or LVPECL drivers to convert the balanced, differential signal into an unbalanced, single-ended signal.

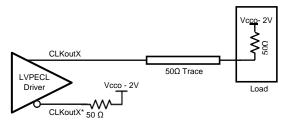

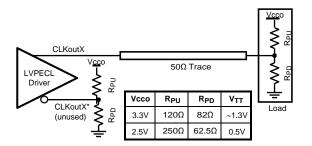

It is possible to use an LVPECL driver as one or two separate 800mV p-p signals. When DC coupling one of the RS00304Q LVPECL driver of a CLKoutX/CLKoutX\* pair, be sure to properly terminate the unused driver. When DC coupling on of the RS00304Q LVPECL drivers, the termination should be  $50\Omega$  to Vcco – 2V. The Thevenin equivalent circuit is also a valid termination for Vcco = 3.3V.

. Single-Ended LVPECL Operation, DC Coupling

Single-Ended LVPECL Operation, DC Coupling, Thevenin Equivalent

When AC coupling an LVPECL driver use a  $160\Omega$  emitter resistor (or  $91\Omega$  for Vcco = 2.5V) to provide a DC path to ground and ensure a  $50\Omega$  termination with the proper DC bias level for the receiver. The typical DC bias voltage for LVPECL receivers is 2V. If the companion driver is not used, it should be terminated with either a proper AC or DC termination. This latter example of AC coupling a single-ended LVPECL signal can be used to measure single-ended LVPECL performance using a spectrum analyzer or phase noise analyzer. When using most RF test equipment no DC bias point (0VDC) is required for safe and proper operation. The internal  $50\Omega$  termination the test equipment correctly terminates the LVPECL driver being measured as shown in the figure. When using only one LVPECL driver of a CLKoutX/CLKoutX\* pair, be sure to properly terminated the unused driver.

Single-Ended LVPECL Operation, AC Coupling

### **Power Supply Recommendations**

#### **Power Supply Sequencing**

When powering the Vcc and Vcco pins from separate supply rails, it is recommended that the supplies to reach their regulation point at approximately the same time while ramping up, or reach ground potential at the same time while ramping down. Using simultaneous or ratio metric power supply sequencing prevents internal current flow from Vcc to Vcco pins that could occur when Vcc is powered before Vcco.

#### **Power Supply Bypassing**

The Vcc and Vcco power supplies should have a high-frequency bypass capacitor, such as  $0.1\mu$ F or  $0.01\mu$ F, placed very close to each supply pin.  $1\mu$ F to  $10\mu$ F decoupling capacitors should also be placed nearby the device between the supply and ground planes. All bypass and decoupling capacitors should have short connections to the supply and ground plane through a short trace or via to minimize series inductance.

## **Package Information**

# **Revision History**

| Revision | Description        | Date       |  |  |

|----------|--------------------|------------|--|--|

| V1.0     | 1. Initial release | 2025/01/21 |  |  |

|          |                    |            |  |  |