## **Features**

- PCIe Gen5 additive phase jitter: 12fs RMS

- PCIe Gen6 additive phase jitter: 5fs RMS

- DB2000QL additive phase jitter: 15fs RMS

- 12kHz to 20MHz additive phase jitter: 33fs RMS at 156.25MHz

- Power Down Tolerant (PDT) inputs

- Flexible Startup Sequencing (FSS)

- Automatic Clock Parking (ACP) upon loss of CLKIN

- Selectable output slew rate via pin or SMBus

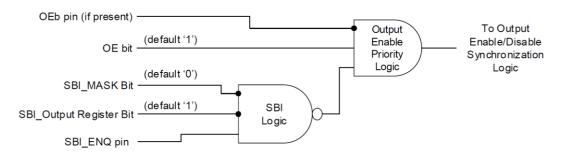

- 4-wire Side-Band Interface supports high-speed

- serial output enable and device daisy-chaining

- 9 selectable SMBus addresses

- SMBus write protection features

- Spread-spectrum tolerant

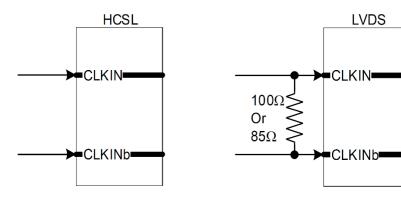

- $85\Omega$  or  $100\Omega$  (-100 suffix) output impedance

- CLKIN accepts HCSL or LVDS signal levels

- -40 to +105°C, 3.3V ±10% 1.8V ±5% operation

## **Applications**

- Cloud/High-performance Computing

- NVMe Storage

- Networking

- Accelerators

## Description

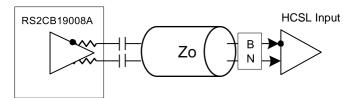

The RS2CB19008A ultra-high performance series fanout buffers support PCIe Gen5 and Gen6. They provide a Loss-Of-Signal (LOS) output for system monitoring and redundancy. The devices also incorporate Power Down Tolerant (PDT) and Flexible Startup Sequencing (FSS) features, easing system design. They can drive both source-terminated and double terminated loads, operating up to 400MHz.

The RS2CB19008A devices offer higher output counts in smaller packages compared to earlier buffer families. The buffers support both Common Clock (CC) and Independent Reference (IR) PCIe clock architectures.

# **Ordering Information**

| Part Number         | Number of<br>Outputs | Differential<br>Output<br>Impedance (Ω) | Package  | Operation<br>Temperature |

|---------------------|----------------------|-----------------------------------------|----------|--------------------------|

| RS2CB19008AZLAE     | 8                    | 85                                      | TQFN-40L | -40 to +105°C            |

| RS2CB19008A-100ZLAE | 8                    | 100                                     |          | -40 10 +103 C            |

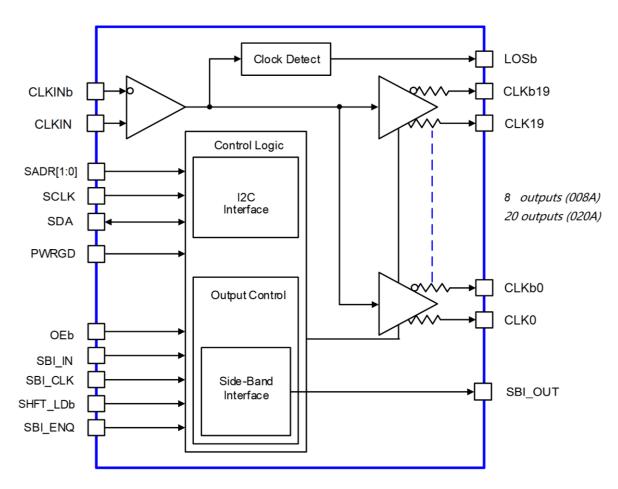

## 1.1 RS2CB19008A Block Diagram

#### Figure 1. RS2CB19008A/020A Block Diagram

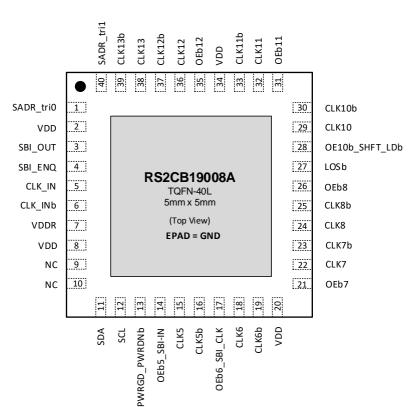

## 1.2 RS2CB19008A Pin Assignments

#### Table 1. RS2CB19008A Pin Descriptions

| Pin<br>Number | Pin Name     | Туре           | Description                                                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------|--------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1             | SADR_tri0    | I, SE, PD, PU  | SMBus address bit. This is a tri-level input that works in conjunction with other SADR pins, if present, to decode SMBus Addresses. See the SMBus Address Decode table and the tri-level input thresholds in the electrical tables.                                                                                                                                                                                             |

| 2             | VDD          | PWR            | Clock power supply.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 3             | SBI_OUT      | I, SE, PD      | Tthe SBI shift register data output. The function is this pin is controlled by the SBI_ENQ. For more information, see Side-Band Interface (SBI).                                                                                                                                                                                                                                                                                |

| 4             | SBI_ENQ      | I, SE, PD, PDT | Input that selects function of pins that are multiplexed between<br>OE and SBI functionality. SMBus output enable bits and non-<br>multiplexed OE pins remain functional when SBI is enabled.<br>This pin must be strapped to its desired state. It cannot<br>dynamically change.<br>0 = SBI is disabled. Multiplexed pins function as output enables.<br>1 = SBI is enabled. Multiplexed pins function as SBI control<br>pins. |

| 5             | CLKIN        | I, DIF         | True clock input.                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6             | CLKINb       | I, DIF         | Complementary clock input.                                                                                                                                                                                                                                                                                                                                                                                                      |

| 7             | VDDR         | PWR            | Power supply for clock input (receiver).                                                                                                                                                                                                                                                                                                                                                                                        |

| 8             | VDD          | PWR            | Clock power supply.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 9             | NC           | PWR            | Not connect                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 10            | NC           | PWR            | Not connect                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 11            | SDA          | I/O, SE, OD    | Data pin for SMBus interface.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 12            | SCL          | I, SE          | Clock pin of SMBus interface.                                                                                                                                                                                                                                                                                                                                                                                                   |

| 13            | PWRGD_PWRDNb | I, SE, PU, PDT | Input notifies device to sample latched inputs and start up on first high assertion. Low enters Power Down Mode, subsequent high assertions exit Power Down Mode.                                                                                                                                                                                                                                                               |

| 14            | OEb5_SBI_IN  | I, SE, PD, PDT | Active low input for enabling output 5 or the clock pin for the<br>SBI shift register. The function is this pin is controlled by the<br>SBI_ENQ pin. For more information, see Side-Band Interface<br>(SBI).<br>OE mode:<br>0 = Enable output, 1 = Disable output. Side-Band mode:<br>Clocks data into the SBI on the rising edge.                                                                                              |

| 15            | CLK5         | O, DIF         | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 16            | CLK5b        | O, DIF         | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 17            | OEb6_SBI_CLK | I, SE, PD, PDT | Active low input for enabling output 5 or the clock pin for the<br>SBI shift register. The function is this pin is controlled by the<br>SBI_ENQ pin. For more information, see Side-Band Interface<br>(SBI).<br>OE mode:<br>0 = Enable output, 1 = Disable output. Side-Band mode:<br>Clocks data into the SBI on the rising edge.                                                                                              |

| 18            | CLK6         | O, DIF         | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                              |

| 19            | CLK6b        | O, DIF         | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                     |

| 20            | VDD          | PWR            | Clock power supply.                                                                                                                                                                                                                                                                                                                                                                                                             |

| 21            | OEb7         | I, SE, PD, PDT | Active low input for enabling output 7. 0 = Enable output, 1 = Disable output.                                                                                                                                                                                                                                                                                                                                                  |

### RS2CB19008A Series Clock Buffer

PCIe Gen5/6 1:8 Fan out Buffer with LOS

| Pin<br>Number | Pin Name       | Туре           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|---------------|----------------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22            | CLK7           | O, DIF         | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 23            | CLK7b          | O, DIF         | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 24            | CLK8           | O, DIF         | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 25            | CLK8b          | O, DIF         | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 26            | OEb8           | I, SE, PD, PDT | Active low input for enabling output 6. 0 = Enable output, 1 = Disable output.                                                                                                                                                                                                                                                                                                                                                                   |

| 27            | LOSb           | O, OD, PDT     | Output indicating Loss of Input Signal. This pin is an open-drain<br>output and requires an external pull-up resistor for proper<br>functionality. A low output on this pin indicates a loss of signal<br>on the input clock.                                                                                                                                                                                                                    |

| 28            | OEb10_SHFT_LDb | I, SE, PD, PDT | Active low input for enabling output 13 or SHFT_LDb pin for the<br>Side-Band Interface. The function of this pin is controlled by the<br>SBI_ENQ pin. For more information, see Side-Band Interface<br>(SBI).<br>OE mode:<br>0 = Enable output, 1 = Disable output. Side-Band mode:<br>0 = Disable SBI shift register, 1 = Enable SBI shift register.<br>A falling edge transfers SBI shift register contents to SBI output<br>control register. |

| 29            | CLK10          | O, DIF         | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 30            | CLK10b         | O, DIF         | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 31            | OEb11          | I, SE, PD, PDT | Active low input for enabling output 11. 0 = Enable output, 1 = Disable output.                                                                                                                                                                                                                                                                                                                                                                  |

| 32            | CLK11          | O, DIF         | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 33            | CLK11b         | O, DIF         | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 34            | VDD            | PWR            | Clock power supply.                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 35            | OEb12          | I, SE, PD, PDT | Active low input for enabling output 12. 0 = Enable output, 1 = Disable output.                                                                                                                                                                                                                                                                                                                                                                  |

| 36            | CLK12          | O, DIF         | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 37            | CLK12b         | O, DIF         | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 38            | CLK13          | O, DIF         | True clock output.                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 39            | CLK13b         | O, DIF         | Complementary clock output.                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 40            | SADR_tri1      | I, SE, PD, PU  | SMBus address bit. This is a tri-level input that works in conjunction with other SADR pins, if present, to decode SMBus Addresses. See the SMBus Address Decode table and the tri-level input thresholds in the electrical tables.                                                                                                                                                                                                              |

| 41            | EPAD           | GND            | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# 2. Specifications

# 2.1 Absolute Maximum Ratings

| Symbol           | Parameter                             | Condition                              | MIN  | MAX                    | Unit |

|------------------|---------------------------------------|----------------------------------------|------|------------------------|------|

| V <sub>DDx</sub> | Supply Voltage with respect to Ground | Any VDD pin                            | -0.5 | 3.9                    | V    |

| V <sub>IN</sub>  | Input Voltage                         | [1]                                    | -0.5 | 3.9                    | V    |

| V <sub>IN</sub>  | Input Voltage                         | [2]                                    | -0.5 | V <sub>DDx</sub> + 0.3 | V    |

| I <sub>IN</sub>  | Input Current                         | All SE inputs and CLKIN <sup>[2]</sup> | -    | <u>+</u> 50            | mA   |

|                  |                                       | CLK                                    | -    | 30                     | mA   |

|                  | Output Current – Continuous           | SDATA, SBI_OUT                         | -    | 25                     | mA   |

| I <sub>OUT</sub> |                                       | CLK                                    | -    | 60                     | mA   |

| 001              | Output Current – Surge                | SDATA, SBI_OUT                         | -    | 50                     | mA   |

| TJ               | Maximum Junction Temperature          | -                                      | -    | 150                    | °C   |

| Τ <sub>S</sub>   | Storage Temperature                   | Storage Temperature                    | -65  | 150                    | °C   |

1. Pins designated Power Down Tolerant (PDT) in the pin description tables.

2. Pins not designated Power Down Tolerant (PDT) in the pin description tables.

## 2.2 ESD Ratings

| Symbol | Parameter            | Condition                                 | Rating | Unit |

|--------|----------------------|-------------------------------------------|--------|------|

| ESD    | Human Body Model     | ANSI/ESDA/JEDECJS-001-2023 Classification | 8000   | V    |

| LOD    | Charged Device Model | ANSI/ESDA/TEDECJS-002-2022 Classification | 1000   | V    |

# 2.3 Recommended Operation Conditions

| Symbol           | Parameter                                                                                           | Condition                                                                                      | MIN  | ТҮР | МАХ  | Unit |

|------------------|-----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|-----|------|------|

| TJ               | Maximum Junction Temperature                                                                        | -                                                                                              | -    | -   | 125  | °C   |

| T <sub>A</sub>   | Ambient Operating Temperature                                                                       | -                                                                                              | -40  | 25  | 105  | ů    |

| V                |                                                                                                     | Any VDD pin, 3.3V ±10% supply.                                                                 | 2.97 | 3.3 | 3.63 | V    |

| V <sub>DDx</sub> | Supply Voltage with respect to Ground                                                               | Any VDD pin, 1.8V ±5% supply.                                                                  | 1.71 | 1.8 | 1.89 | V    |

| t <sub>PU</sub>  | Power-up time for all VDDs to reach<br>minimum specified voltage (power<br>ramps must be monotonic) | Power-up time for all VDDs to reach minimum specified voltage (power ramps must be monotonic). | 0.05 | -   | 5    | ms   |

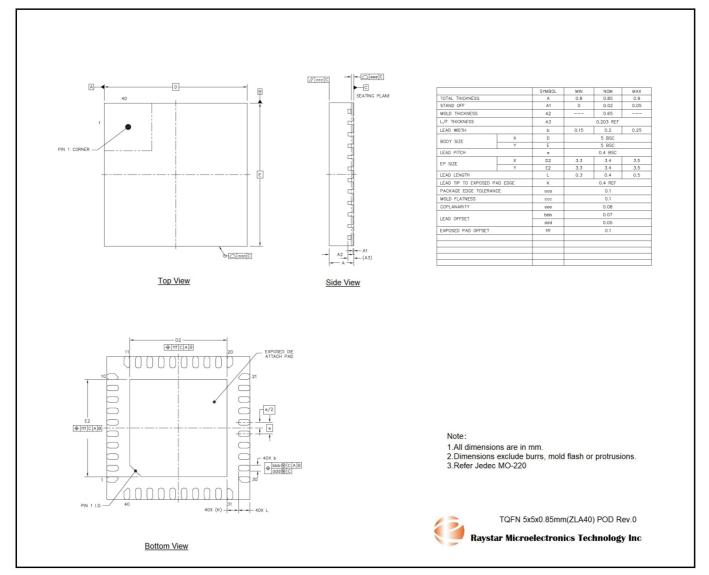

## 2.4 Thermal Information

| Package <sup>[1]</sup> | Symbol           | Condition                       | Typical Value (°C/W) |

|------------------------|------------------|---------------------------------|----------------------|

|                        | θ <sub>Jc</sub>  | Junction to Case                | 44                   |

|                        | θ <sub>Jb</sub>  | Junction to Base                | 2                    |

| 5 × 5 mm TQFN-40L      | θ <sub>JA0</sub> | Junction to Air, still air      | 33                   |

| (3.4 × 3.4 mm ePad)    | θ <sub>JA1</sub> | Junction to Air, 1 m/s air flow | 29                   |

|                        | θ <sub>JA3</sub> | Junction to Air, 3 m/s air flow | 28                   |

|                        | $\theta_{JA5}$   | Junction to Air, 5 m/s air flow | 27                   |

1. ePad soldered to board.

## 2.5 Electrical Characteristics

### 2.5.1 Phase Jitter

#### Table 2. PCIe Refclk Phase Jitter - Normal Conditions<sup>[1][2][3][8]</sup>

| Symbol                     | Parameter                                      | Condition                     | ТҮР | МАХ   | Specification<br>Limit | Unit     |

|----------------------------|------------------------------------------------|-------------------------------|-----|-------|------------------------|----------|

| t <sub>jphPCleG1-CC</sub>  |                                                | PCle Gen1 (2.5 GT/s)          | 610 | 15000 | 86000 [6]              | fs p-p   |

| +                          |                                                | PCIe Gen2 Hi Band (5.0 GT/s)  | 120 | 310   | 3,100 <sup>[6]</sup>   |          |

| <sup>t</sup> jphPCleG2-CC  | Additive PCIe Phase Jitter                     | PCIe Gen2 Lo Band (5.0 GT/s)  | 10  | 20    | 3,000 [6]              |          |

| t <sub>jphPCleG3-CC</sub>  | (Common Clocked Architecture)                  | PCIe Gen3 (8.0 GT/s)          | 15  | 25    | 1,000 <sup>[6]</sup>   | fs RMS   |

| t <sub>jphPCleG4-CC</sub>  | SSC ≤ -0.5%                                    | PCIe Gen4 (16.0 GT/s) [3] [4] | 15  | 25    | 500 [6]                | IS RIVIO |

| t <sub>jphPCleG5-CC</sub>  |                                                | PCIe Gen5 (32.0 GT/s) [3] [5] | 12  | 25    | 150 [6]                |          |

| t <sub>jphPCleG6-CC</sub>  |                                                | PCIe Gen6 (64.0 GT/s) [3] [5] | 5   | 18    | 100 [6]                |          |

| t <sub>jphPCleG2-IR</sub>  |                                                | PCIe Gen2 (5.0 GT/s)          | 80  | 300   |                        |          |

| t <sub>jphPCle</sub> G3-IR | Additive PCIe Phase Jitter                     | PCIe Gen3 (8.0 GT/s)          | 50  | 150   |                        |          |

| t <sub>jphPCleG4-IR</sub>  | (IR Architectures - SRIS, SRNS)<br>SSC ≤ -0.3% | PCIe Gen4 (16.0 GT/s) [3] [4] | 40  | 100   | [7]                    | fs RMS   |

| t <sub>jphPCleG5-IR</sub>  |                                                | PCIe Gen5 (32.0 GT/s) [3] [5] | 15  | 30    |                        |          |

| t <sub>jphPCleG6-IR</sub>  |                                                | PCIe Gen6 (64.0 GT/s) [3] [5] | 12  | 30    |                        |          |

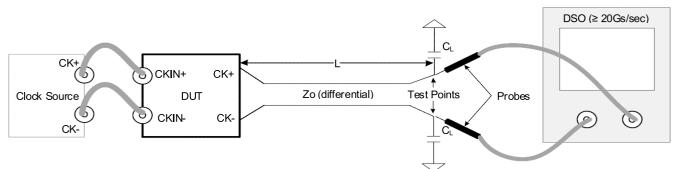

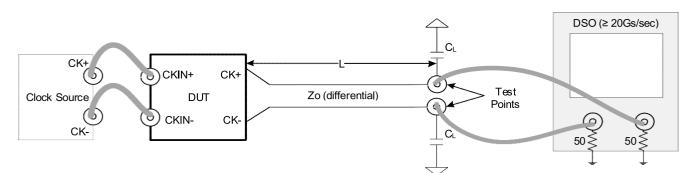

- 1. The Refclk jitter is measured after applying the filter functions found in the *PCI Express Base Specification 6.0, Revision 1.0.* For the exact measurement setup, see Test Loads. The worst case results for each data rate are summarized in this table. Equipment noise is removed from all measurements.

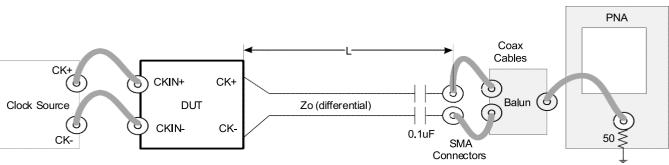

- 2. Jitter measurements should be made with a capture of at least 100,000 clock cycles captured by a real-time oscilloscope (RTO) with a sample rate of 20GS/s or greater. Broadband oscilloscope noise must be minimized in the measurement. The measured PP jitter is used (no extrapolation) for RTO measurements. Alternately, jitter measurements can be used with a Phase Noise Analyzer (PNA) extending (flat) and integrating and folding the frequency content up to an offset from the carrier frequency of at least 200MHz (at 300MHz absolute frequency) below the Nyquist frequency. For PNA measurements for the 2.5GT/s data rate, the RMS jitter is converted to peak-to-peak jitter using a multiplication factor of 8.83.

- 3. SSC spurs from the fundamental and harmonics are removed up to a cutoff frequency of 2MHz taking care to minimize removal of any non-SSC content.

- 4. Note that 0.7ps RMS is to be used in channel simulations to account for additional noise in a real system.

- 5. Note that 0.25ps RMS is to be used in channel simulations to account for additional noise in a real system.

- 6. The rms sum of the source jitter and the additive jitter (arithmetic sum for PCIe Gen1) must be less than the jitter specification listed.

- 7. The PCI Express Base Specification 6.0, Revision 1.0 provides the filters necessary to calculate SRIS jitter values; it does not provide specification limits, therefore, the reference to this footnote in the Limit column. SRIS values are informative only. A common practice is to split the common clock budget in half. For 16GT/s data rates and above, the user must choose whether to use the output jitter specification, or the input jitter specification, which includes an allocation for the jitter added by the channel. Using 32GT/s, the Refclk jitter budget is 150fs RMS. One half of the Refclk jitter budget is 106fs RMS. At the clock input, the system must deliver 250fs RMS. One half of this value is 177fs RMS. If the clock is placed next to the PCIe device in an SRIS system, the channel is very short and the user can choose to use this more relaxed value as the jitter limit.

- 8. Differential input swing  $\geq$  1600mV and input slew rate  $\geq$  3.5V/ns

| Symbol                    | Parameter                       | Condition                    | ТҮР | МАХ | Specification<br>Limit | Unit     |

|---------------------------|---------------------------------|------------------------------|-----|-----|------------------------|----------|

| t <sub>jphPCleG1-CC</sub> |                                 | PCIe Gen1 (2.5 GT/s)         | 692 | 839 | 86,000 <sup>[6]</sup>  | fs p-p   |

|                           |                                 | PCIe Gen2 Hi Band (5.0 GT/s) | 41  | 49  | 3,100 <sup>[6]</sup>   |          |

| t <sub>jphPCleG2-CC</sub> | Additive PCIe Phase Jitter      | PCIe Gen2 Lo Band (5.0 GT/s) | 11  | 14  | 3,000 [6]              | -        |

| t <sub>jphPCleG3-CC</sub> | (Common Clocked Architecture)   | PCIe Gen3 (8.0 GT/s)         | 20  | 24  | 1,000 <sup>[6]</sup>   | fs RMS   |

| t <sub>jphPCleG4-CC</sub> | SSC ≤ -0.5%                     | PCIe Gen4 (16.0 GT/s) [3][4] | 20  | 24  | 500 [6]                | 13 1 100 |

| t <sub>jphPCleG5-CC</sub> |                                 | PCIe Gen5 (32.0 GT/s) [3][5] | 8   | 9.3 | 150 <sup>[6]</sup>     |          |

| t <sub>jphPCleG6-CC</sub> |                                 | PCIe Gen6 (64.0 GT/s) [3][5] | 5   | 6   | 100 [6]                |          |

| t <sub>jphPCleG2-IR</sub> |                                 | PCIe Gen2 (5.0 GT/s)         | 52  | 63  |                        |          |

| t <sub>jphPCleG3-IR</sub> | Additive PCIe Phase Jitter      | PCIe Gen3 (8.0 GT/s)         | 14  | 17  |                        |          |

| t <sub>jphPCleG4-IR</sub> | (IR Architectures - SRIS, SRNS) | PCIe Gen4 (16.0 GT/s) [3][4] | 14  | 17  |                        | fs RMS   |

| t <sub>jphPCleG5-IR</sub> | SSC ≤ -0.3%                     | PCIe Gen5 (32.0 GT/s) [3][5] | 12  | 15  | [7]                    |          |

| t <sub>jphPCleG6-IR</sub> |                                 | PCIe Gen6 (64.0 GT/s) [3][5] | 15  | 19  |                        |          |

#### Table 3. PCIe Refclk Phase Jitter - Degraded Conditions<sup>[1][2][3][8]</sup>

1. The Refclk jitter is measured after applying the filter functions found in the *PCI Express Base Specification 6.0, Revision 1.0.* For the exact measurement setup, see Test Loads. The worst case results for each data rate are summarized in this table. Equipment noise is removed from all measurements.

- 2. Jitter measurements should be made with a capture of at least 100,000 clock cycles captured by a real-time oscilloscope (RTO) with a sample rate of 20GS/s or greater. Broadband oscilloscope noise must be minimized in the measurement. The measured PP jitter is used (no extrapolation) for RTO measurements. Alternately, jitter measurements may be used with a Phase Noise Analyzer (PNA) extending (flat) and integrating and folding the frequency content up to an offset from the carrier frequency of at least 200MHz (at 300MHz absolute frequency) below the Nyquist frequency. For PNA measurements for the 2.5GT/s data rate, the RMS jitter is converted to peak-to-peak jitter using a multiplication factor of 8.83.

- 3. SSC spurs from the fundamental and harmonics are removed up to a cutoff frequency of 2MHz taking care to minimize removal of any non-SSC content.

- 4. Note that 0.7ps RMS is to be used in channel simulations to account for additional noise in a real system.

- 5. Note that 0.25ps RMS is to be used in channel simulations to account for additional noise in a real system.

- 6. The rms sum of the source jitter and the additive jitter (arithmetic sum for PCIe Gen1) must be less than the jitter specification listed.

- 7. The PCI Express Base Specification 6.0, Revision 1.0 provides the filters necessary to calculate SRIS jitter values; it does not provide specification limits, therefore, the reference to this footnote in the Limit column. SRIS values are informative only. A common practice is to split the common clock budget in half. For 16GT/s data rates and above, the user must choose whether to use the output jitter specification, or the input jitter specification, which includes an allocation for the jitter added by the channel. Using 32GT/s, the Refclk jitter budget is 150fs RMS. One half of the Refclk jitter budget is 106fs RMS. At the clock input, the system must deliver 250fs RMS. One half of this value is 177fs RMS. If the clock is placed next to the PCIe device in an SRIS system, the channel is very short and the user may choose to use this more relaxed value as the jitter limit.

- 8. Differential input swing = 800mV and input slew rate = 1.5V/ns

| Table 4 | Non-PCle | Refclk | Phase | Jitter | [1][2][3] |

|---------|----------|--------|-------|--------|-----------|

|---------|----------|--------|-------|--------|-----------|

| Symbol      | Parameter                          | Condition                                    | ТҮР | МАХ | Specification<br>Limit | Unit   |

|-------------|------------------------------------|----------------------------------------------|-----|-----|------------------------|--------|

| tjphDB2000Q | Additive Phase Jitter - normal     | 100MHz, Intel-supplied filter [3]            | 10  | 12  | 80 [5]                 |        |

| tjph12k-20M | conditions <sup>[4]</sup>          | 156.25MHz (12kHz to 20MHz)                   | 30  | 36  | N/A                    |        |

| tjphDB2000Q | Additive Phase Jitter -            | 100MHz, Intel-supplied filter <sup>[3]</sup> | 13  | 16  | 80 [5]                 | fs RMS |

| tjph12k-20M | degraded conditions <sup>[6]</sup> | 156.25MHz (12kHz to 20MHz)                   | 39  | 48  | N/A                    |        |

1. See Test Loads for test configuration.

2. SMA100B used as signal source.

3. The RS2CB19008A devices meet all legacy QPI/UPI specifications by meeting the PCIe and DB2000Q specifications listed in this document.

4. Differential input swing = 1,600 mV and input slew rate = 3.5 V/ns.

5. The rms sum of the source jitter and the additive jitter (arithmetic sum for PCIe Gen1) must be less than the jitter specification listed.

6. Differential input swing = 800mV and input slew rate = 1.5V/ns.

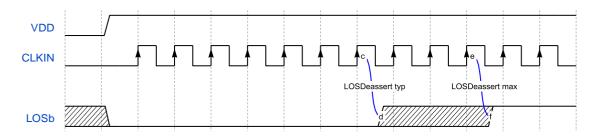

## 2.5.2 Output Frequencies, Startup Time, and LOS Timing

| Table 5. Output Frequencies | . Startup Time | and LOS Timing       |

|-----------------------------|----------------|----------------------|

| Table of Calpart requeitero | , otaitap inno | , ana <b>200</b> mmg |

| Symbol                   | Parameter           | Condition                                                                             | MIN | ТҮР | ΜΑΧ | Unit   |

|--------------------------|---------------------|---------------------------------------------------------------------------------------|-----|-----|-----|--------|

| f                        | Operating Frequency | Automatic Clock Parking (ACP) Circuit disabled                                        | 1   | -   | 400 | MHz    |

| f <sub>OP</sub>          |                     | Automatic Clock Parking (ACP) Circuit enabled                                         | 25  | -   | 400 | IVITIZ |

| t <sub>STARTUP</sub>     | Start-up Time       | [1]                                                                                   | -   | 1.2 | 3   | ms     |

| t <sub>STARTUP</sub>     | Start-up Time       | [2]                                                                                   | -   | 0.3 | 1   | ms     |

| t <sub>LATOEb</sub>      | OEb latency         | OEb assertion/de-assertion CLK<br>start/stop latency. Input clock must be<br>running. | 4   | 5   | 10  | clks   |

| t <sub>LOSAssert</sub>   | LOS Assert Time     | Time from disappearance of input clock to LOS assert. <sup>[3][4]</sup>               | -   | 123 | 200 | ns     |

| t <sub>LOSDeassert</sub> | LOS De-assert Time  | Time from appearance of input clock to LOS de-assert. <sup>[3][5]</sup>               | -   | 6   | 9   | clks   |

1. Measured from when all power supplies have reached > 90% of nominal voltage to the first stable clock edge on the output. PWRGD\_PWRDNb tied to VDD in this case.

2. VDD stable, measured from de-assertion of PWRGD\_PWRDNb.

3. The clock detect circuit does not qualify the accuracy of the input clock. The first input clock must appear to release the power on reset and enable the LOS circuit at power up.

- 4. PWRGD\_PWRDNb high. The Automatic Clock Parking (ACP) circuit if enabled will park the outputs in a low/low state within this time. See Byte4, bit 4 LOSb\_ACP\_ENABLE.

- 5. PWRGD\_PWRDNb high. The device will drive the outputs to a high/low state within this time and then begin clocking the outputs

## 2.5.3 RS2CB19008A CLK AC/DC Output Characteristics

Table 6. RS2CB19008A 85Ω CLK AC/DC Characteristics - Source-Terminated 100MHz PCIe <sup>[1]</sup>

| Symbol              | Parameter                                                                         | Conditions                                                      | MIN  | ТҮР | МАХ  | Specification<br>Limit <sup>[2]</sup> | Unit         |

|---------------------|-----------------------------------------------------------------------------------|-----------------------------------------------------------------|------|-----|------|---------------------------------------|--------------|

| V <sub>MAX</sub>    | Absolute Max Voltage<br>Includes 300mV of<br>Overshoot (Vovs) <sup>[3][4]</sup>   | Across all settings in this                                     | -    | -   | 1092 | 1150                                  |              |

| V <sub>MIN</sub>    | Absolute Min Voltage<br>Includes -300mV of<br>Undershoot (Vuds) <sup>[3][5]</sup> | table at 100MHz.                                                | -166 | -   | -    | -300                                  |              |

| V <sub>HIGH</sub>   | Voltage High [3]                                                                  | V <sub>HIGH</sub> set to 800mV.                                 | 678  | 819 | 994  | -                                     | mV           |

| V <sub>LOW</sub>    | Voltage Low <sup>[3]</sup>                                                        | VHIGH Set to boomv.                                             | -88  | 29  | 146  | -                                     |              |

| V <sub>CROSS</sub>  | Crossing Voltage (abs)<br>[3][6][7]                                               | V <sub>HIGH</sub> set to 800mV,                                 | 278  | 403 | 543  | 250 to 550                            |              |

| ΔV <sub>CROSS</sub> | Crossing Voltage (var)<br>[3][6][8]                                               | scope averaging off.                                            | -    | 1   | 97   | 140                                   |              |

| -1 / -14            |                                                                                   | V <sub>HIGH</sub> set to 800mV, Fast slew rate, scope averaging | 2.0  | 2.8 | 4.0  | 2 to 5                                | ) <i>(/-</i> |

| dv/dt               | Slew Rate <sup>[9][10]</sup>                                                      | V <sub>HIGH</sub> set to 800mV, Slow slew rate, scope averaging | 1.6  | 2.2 | 3.3  | 1.5 to 3.5                            | V/ns         |

| ΔT <sub>R/F</sub>   | Rise/Fall Matching <sup>[3] [11]</sup>                                            | V <sub>HIGH</sub> set to 800mV. Fast<br>slew rate.              | -    | 4   | 19   | 20                                    | %            |

|                    |                                       | V <sub>HIGH</sub> set to 800mV. Slow slew rate.                 | -    | 6    | 24   | N/A        |      |

|--------------------|---------------------------------------|-----------------------------------------------------------------|------|------|------|------------|------|

| V <sub>HIGH</sub>  | Voltage High <sup>[3]</sup>           | V <sub>HIGH</sub> set to 900mV.                                 | 719  | 903  | 1090 | -          |      |

| $V_{LOW}$          | Voltage Low <sup>[3]</sup>            | VHIGH Set to Sooniv.                                            | -115 | 37   | 163  | -          |      |

| V <sub>CROSS</sub> | Crossing Voltage (abs) <sup>[3]</sup> | V <sub>HIGH</sub> set to 900mV,                                 | 289  | 445  | 582  | 250 to 600 | mV   |

| $\Delta V_{CROSS}$ | Crossing Voltage (var) <sup>[3]</sup> | scope averaging off.                                            | -    | 1    | 105  | 140        |      |

|                    | Slew Rate <sup>[9][10]</sup>          | V <sub>HIGH</sub> set to 900mV, Fast slew rate, scope averaging | 2.1  | 2.9  | 4.3  | 2 to 5     |      |

| dv/dt              |                                       | V <sub>HIGH</sub> set to 900mV, Slow slew rate, scope averaging | 1.7  | 2.3  | 3.5  | 1.5 to 3.5 | V/ns |

| A.T.               |                                       | V <sub>HIGH</sub> set to 900mV. Fast slew rate.                 | -    | 5    | 18   | 20         |      |

| ΔT <sub>R/F</sub>  | Rise/Fall Matching <sup>[3][11]</sup> | V <sub>HIGH</sub> set to 900mV. Slow slew rate.                 | -    | 6    | 26   | N/A        | %    |

| t <sub>DC</sub>    | Output Duty Cycle [9]                 | V <sub>T</sub> = 0V differential. 50%<br>duty cycle input.      | 49   | 49.9 | 51   | 45 to 55   | %    |

1. Standard high impedance load with  $C_L = 2pF$ . See Test Loads.

2. The specification limits are taken from either the *PCle Base Specification Revision 6.0* or from relevant x86 processor specifications, whichever is more stringent.

3. Measured from single-ended waveform.

4. Defined as the maximum instantaneous voltage including overshoot.

5. Defined as the minimum instantaneous voltage including undershoot.

6. Measured at crossing point where the instantaneous voltage value of the rising edge of REFCLK+ equals the falling edge of REFCLK-.

- 7. Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossing points for this measurement.

- 8. Defined as the total variation of all crossing voltages of Rising REFCLK+ and Falling REFCLK-. This is the maximum allowed variance in VCROSS for any particular system.

- 9. Measured from differential waveform.

- 10. Measured from -150 mV to +150 mV on the differential waveform (derived from REFCLK+ minus REFCLK-). The signal must be monotonic through the measurement region for rise and fall time. The 300 mV measurement window is centered on the differential zero crossing.

- 11. Matching applies to rising edge rate for REFCLK+ and falling edge rate for REFCLK-. It is measured using a ±75 mV window centered on the median cross point where REFCLK+ rising meets REFCLK- falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The Rise Edge Rate of REFCLK+ should be compared to the Fall Edge Rate of REFCLK-; the maximum allowed difference should not exceed 20% of the slowest edge rate.

| Table 7. RS2CB19008A 100Ω CLK AC/DC C | haracteristics - Source-Terminated 100MHz PCIe Apps <sup>[1]</sup> |

|---------------------------------------|--------------------------------------------------------------------|

|---------------------------------------|--------------------------------------------------------------------|

| Symbol            | Parameter                                                                         | Condition                                    | MIN  | ТҮР | МАХ  | Specification<br>Limit <sup>[2]</sup> | Unit |

|-------------------|-----------------------------------------------------------------------------------|----------------------------------------------|------|-----|------|---------------------------------------|------|

| V <sub>MAX</sub>  | Absolute Max Voltage<br>Includes 300mV of<br>Overshoot (Vovs) <sup>[3][4]</sup>   |                                              | -    | -   | 1050 | 1150                                  | mV   |

| V <sub>MIN</sub>  | Absolute Min Voltage<br>Includes -300mV of<br>Undershoot (Vuds) <sup>[3][5]</sup> | Across all settings in this table at 100MHz. | -150 | -   | -    | -300                                  | TIV  |

| V <sub>HIGH</sub> | Voltage High <sup>[3]</sup>                                                       | V <sub>HIGH</sub> set to 800mV.              | 710  | 815 | 915  | -                                     | mV   |

| V <sub>LOW</sub>  | Voltage Low [3]                                                                   | VHIGH SET TO ODDITIV.                        | -35  | 20  | 75   | -                                     | 111V |

|                     | 1                                                          | 1                                                                   | 1   |     |      | 1          |      |  |

|---------------------|------------------------------------------------------------|---------------------------------------------------------------------|-----|-----|------|------------|------|--|

| V <sub>CROSS</sub>  | Crossing Voltage (abs) <sup>[3]</sup>                      | V <sub>HIGH</sub> set to 800mV, scope                               | 285 | 410 | 500  | 250 to 550 |      |  |

| ΔV <sub>CROSS</sub> | Crossing Voltage (var) <sup>[3]</sup><br>[6][8]            | averaging off.                                                      | -25 | 35  | 105  | 140        |      |  |

|                     |                                                            | V <sub>HIGH</sub> set to 800mV, Fast slew rate, scope averaging on. | 2.1 | 3   | 3.7  | 2 to 4     |      |  |

| dv/dt               | Slew Rate <sup>[9][10]</sup>                               | V <sub>HIGH</sub> set to 800mV, Slow slew rate, scope averaging on. | 1.6 | 2.6 | 3.4  | 1.5 to 3.5 | V/ns |  |

| $\Delta T_{R/F}$    | Rise/Fall Matching <sup>[3][11]</sup>                      | V <sub>HIGH</sub> set to 800mV. Fast slew rate.                     | -   | 4   | 16   | 20         | %    |  |

| ΔT <sub>R/F</sub>   | Rise/Fall Matching <sup>[3][11]</sup>                      | V <sub>HIGH</sub> set to 800mV. Slow slew rate.                     | -   | 3.5 | 15.5 | 20         | %    |  |

| V <sub>HIGH</sub>   | Voltage High <sup>[3]</sup>                                | V <sub>HIGH</sub> set to 900mV.                                     | 802 | 907 | 1012 | -          |      |  |

| $V_{LOW}$           | Voltage Low [3]                                            | VHIGH Set to 900mv.                                                 | -38 | 21  | 80   | -          |      |  |

| V <sub>CROSS</sub>  | Crossing Voltage (abs) <sup>[3]</sup>                      | V <sub>HIGH</sub> set to 900mV, scope                               | 320 | 450 | 540  | 300 to 600 | mV   |  |

| ΔV <sub>CROSS</sub> | Crossing Voltage (var) <sup>[3]</sup><br><sup>[6][8]</sup> | averaging off.                                                      | -35 | 40  | 115  | 140        |      |  |

|                     |                                                            | V <sub>HIGH</sub> set to 900mV, Fast slew rate, scope averaging on. | 2.1 | 3.0 | 3.9  | 2 to 4     |      |  |

| dv/dt               | Slew Rate <sup>[9][10]</sup>                               | V <sub>HIGH</sub> set to 900mV, Slow slew rate, scope averaging on. | 1.6 | 2.8 | 3.4  | 1.5 to 3.5 | V/ns |  |

| $\Delta T_{R/F}$    | Rise/Fall Matching [3][11]                                 | V <sub>HIGH</sub> set to 900mV. Fast slew rate.                     | -   | 5   | 19.7 | 20         | %    |  |

| T <sub>R/F</sub>    | Rise/Fall Matching [3][11]                                 | V <sub>HIGH</sub> set to 900mV. Slow slew rate.                     | -   | 4.9 | 19.5 | 20         | %    |  |

| t <sub>DC</sub>     | Output Duty Cycle [9]                                      | V <sub>T</sub> = 0V differential.                                   | 48  | 50  | 52   | 45 to 55   | %    |  |

1. Standard high impedance load with  $C_L=2pF$ . For more information, see Test Loads.

- 2. The specification limits are taken from either the *PCle Base Specification Revision 6.0* or from relevant **x86** processor specifications, whichever is more stringent.

- 3. Measured from single-ended waveform.

- 4. Defined as the maximum instantaneous voltage including overshoot.

- 5. Defined as the minimum instantaneous voltage including undershoot.

- 6. Measured at crossing point where the instantaneous voltage value of the rising edge of REFCLK+ equals the falling edge of REFCLK-.

- 7. Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossing points for this measurement.

- 8. Defined as the total variation of all crossing voltages of Rising REFCLK+ and Falling REFCLK-. This is the maximum allowed variance in VCROSS for any particular system.

- 9. Measured from differential waveform.

- 10. Measured from -150mV to +150mV on the differential waveform (derived from REFCLK+ minus REFCLK-). The signal must be monotonic through the measurement region for rise and fall time. The 300mV measurement window is centered on the differential zero crossing.

- 11. Matching applies to rising edge rate for REFCLK+ and falling edge rate for REFCLK-. It is measured using a ±75mV window centered on the median cross point where REFCLK+ rising meets REFCLK- falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations. The Rise Edge Rate of REFCLK+ should be compared to the Fall Edge Rate of REFCLK-; the maximum allowed difference should not exceed 20% of the slowest edge rate.

| Symbol          | Parameter                                 | Conditions                                                    | MIN  | ТҮР | MAX  | Unit |

|-----------------|-------------------------------------------|---------------------------------------------------------------|------|-----|------|------|

| VOH             | Output High Voltage [2]                   |                                                               | 630  | 800 | 1003 |      |

| VOL             | Output Low Voltage [2]                    | Vнідн = 800mV, Fast Slew Rate, 25MHz,<br>156.25MHz, 312.5MHz. | -150 | 15  | 160  |      |

| VCROSS          | Crossing Voltage (abs) [3]                |                                                               | 230  | 395 | 570  | mV   |

| ΔVCROS<br>S     | Crossing Voltage (var) [3][4][5]          |                                                               | -    | 50  | 140  |      |

| tR              | Rise Time [2]<br>VT = 20% to 80% of swing |                                                               | 135  | 480 | 780  | ps   |

| tF              | Fall Time [2]<br>VT = 20% to 80% of swing |                                                               | 155  | 425 | 748  | ps   |

| VOH             | Output High Voltage [2]                   |                                                               | 700  | 890 | 1100 |      |

| VOL             | Output Low Voltage [2]                    |                                                               | -155 | 30  | 195  |      |

| VCROSS          | Crossing Voltage (abs) [3]                |                                                               | 260  | 430 | 640  | mV   |

| ΔVCROS<br>S     | Crossing Voltage (var) [3][4][5]          | VHIGH = 900mV, Fast Slew Rate, 25MHz,                         | -    | 40  | 165  |      |

| tR              | Rise Time [2]<br>VT = 20% to 80% of swing | 156.25MHz, 312.5MHz.                                          | 160  | 500 | 870  | ps   |

| tF              | Fall Time [2]<br>VT = 20% to 80% of swing |                                                               | 150  | 430 | 765  | ps   |

| t <sub>DC</sub> | Output Duty Cycle [6]                     | Across all settings in this table, VT = 0V.                   | 47   | 50  | 52   | %    |

#### Table 8. RS2CB19008A 85Ω CLK AC/DC Characteristics - Non-PCIe, Source-Terminated Loads [1]

Standard high impedance load with CL = 2pF. See Test Loads.

Measured from single-ended waveform.

3. Measured at crossing point where the instantaneous voltage value of the rising edge of CLK equals the falling edge of CLKb.

4. Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossing points for this measurement. Defined as the total variation of all crossing voltages of Rising CLK and Falling CLKb. This is the maximum allowed variance in VCROSS

5. for any particular system.

6. Measured from differential waveform.

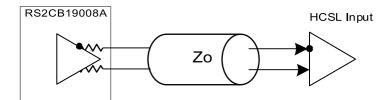

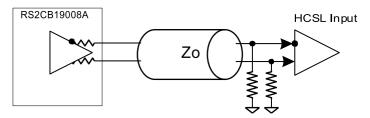

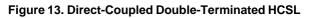

#### Table 9. RS2CB19008A 85Ω CLK AC/DC Characteristics - Non-PCle. Double-Terminated Loads <sup>[1]</sup>

|                    | Table 3. KS2CD 19000A 0522 CER AC/DC Characteristics - Non-Ficle, Double-Terminated Loads 1-1 |                                                                                            |      |     |     |        |  |  |  |  |

|--------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|------|-----|-----|--------|--|--|--|--|

| Symbol             | Parameter                                                                                     | Conditions                                                                                 | MIN  | ТҮР | MAX | Unit   |  |  |  |  |

| V <sub>OH</sub>    | Output High Voltage [2]                                                                       |                                                                                            | 370  | 430 | 475 |        |  |  |  |  |

| V <sub>OL</sub>    | Output Low Voltage [2]                                                                        |                                                                                            | -30  | 11  | 60  | mV     |  |  |  |  |

| V <sub>CROSS</sub> | Crossing Voltage (abs) <sup>[3]</sup>                                                         | V <sub>HIGH</sub> = 800mV, Fast Slew Rate,                                                 | 150  | 215 | 245 | mv     |  |  |  |  |

| $\Delta V_{CROSS}$ | Crossing Voltage (var) [3][4][5]                                                              | 25MHz, 156.25MHz, 312.5MHz<br>(amplitude is reduced by ~50% due to<br>double termination). | -    | 8   | 40  |        |  |  |  |  |

| +_                 | Rise Time <sup>[2]</sup>                                                                      |                                                                                            | 205  | 320 | 570 | ps     |  |  |  |  |

| t <sub>R</sub>     | $V_T = 20\%$ to 80% of swing                                                                  |                                                                                            | 205  | 320 | 570 | μs     |  |  |  |  |

|                    | Fall Time <sup>[2]</sup>                                                                      |                                                                                            | 100  | 200 | 450 |        |  |  |  |  |

| t <sub>F</sub>     | $V_T = 20\%$ to 80% of swing                                                                  |                                                                                            | 120  | 300 | 450 | ps     |  |  |  |  |

| V <sub>OH</sub>    | Output High Voltage [2]                                                                       |                                                                                            | 385  | 490 | 555 |        |  |  |  |  |

| V <sub>OL</sub>    | Output Low Voltage [2]                                                                        |                                                                                            | -30  | 12  | 60  | mV     |  |  |  |  |

| V <sub>CROSS</sub> | Crossing Voltage (abs) <sup>[3]</sup>                                                         | V <sub>HIGH</sub> = 900mV, Fast Slew Rate,                                                 | 170  | 220 | 265 | - 111V |  |  |  |  |

| $\Delta V_{CROSS}$ | Crossing Voltage (var) [3][4][5]                                                              | 25MHz, 100MHz, 156.25MHz,                                                                  | -    | 8   | 45  |        |  |  |  |  |

|                    | Rise Time <sup>[2]</sup>                                                                      | 312.5MHz (amplitude is reduced by ~50% due to double termination).                         | 045  | 000 | 010 |        |  |  |  |  |

| t <sub>R</sub>     | $V_T = 20\%$ to 80% of swing                                                                  |                                                                                            | 215  | 330 | 610 | ps     |  |  |  |  |

|                    | Fall Time [2]                                                                                 | 1                                                                                          | 4.40 | 240 | 100 |        |  |  |  |  |

| t <sub>F</sub>     | $V_T = 20\%$ to 80% of swing                                                                  |                                                                                            | 140  | 310 | 400 | ps     |  |  |  |  |

### RS2CB19008A Series Clock Buffer

PCIe Gen5/6 1:8 Fan out Buffer with LOS

| t <sub>DC</sub> | Output Duty Cycle [6] | Across all settings in this table, $V_T = 0V$ . | 49 | 50 | 51 | % |  |

|-----------------|-----------------------|-------------------------------------------------|----|----|----|---|--|

|-----------------|-----------------------|-------------------------------------------------|----|----|----|---|--|

- 1. Both Tx and Rx are terminated (double-terminated) with CL = 2pF. This reduces amplitude by 50%. See Test Loads.

- 2. Measured from single-ended waveform.

- Measured at crossing point where the instantaneous voltage value of the rising edge of CLK equals the falling edge of CLKb.

Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossing

- Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossin points for this measurement.

- 5. Defined as the total variation of all crossing voltages of Rising CLK and Falling CLKb. This is the maximum allowed variance in VCROSS for any particular system.

- Measured from differential waveform.

7.

#### Table 10. RS2CB19008A 100Ω CLK AC/DC Characteristics - Non-PCIe Apps, Source-Terminated Loads <sup>[1]</sup>

| Symbol             | Parameter                                            | Condition                                                                                                                 | MIN | TYP | МАХ  | Unit |

|--------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|-----|-----|------|------|

| V <sub>OH</sub>    | Output High Voltage [2]                              |                                                                                                                           | 700 | 795 | 910  |      |

| V <sub>OL</sub>    | Output Low Voltage [2]                               | VHIGH = 800mV, Fast Slew Rate,<br>156.25MHz, 312.5MHz.<br>(Slow slew rate is not recommended for<br>frequencies > 100MHz) | -70 | 30  | 120  |      |

| V <sub>CROSS</sub> | Crossing Voltage (abs) <sup>[3]</sup>                |                                                                                                                           | 252 | 375 | 495  | mV   |

| $\Delta V_{CROSS}$ | Crossing Voltage (var) [3][4][5]                     |                                                                                                                           | 0   | 35  | 135  |      |

| t <sub>R</sub>     | Rise Time <sup>[2]</sup><br>VT = 20% to 80% of swing |                                                                                                                           | 205 | 320 | 590  | ps   |

| t <sub>F</sub>     | Fall Time <sup>[2]</sup><br>VT = 20% to 80% of swing |                                                                                                                           | 145 | 315 | 585  | ps   |

| V <sub>OH</sub>    | Output High Voltage <sup>[2]</sup>                   |                                                                                                                           | 750 | 885 | 1020 |      |

| V <sub>OL</sub>    | Output Low Voltage [2]                               |                                                                                                                           | -80 | 20  | 145  | mV   |

| V <sub>CROSS</sub> | Crossing Voltage (abs) <sup>[3]</sup>                | VHIGH = 900mV, Fast Slew Rate,                                                                                            | 260 | 400 | 545  | 1110 |

| $\Delta V_{CROSS}$ | Crossing Voltage (var) [3][4][5]                     | 156.25MHz, 312.5MHz.<br>(Slow slew rate is not recommended for                                                            | 0   | 45  | 145  |      |

| t <sub>R</sub>     | Rise Time <sup>[2]</sup><br>VT = 20% to 80% of swing | frequencies > 100MHz)                                                                                                     | 200 | 390 | 610  | ps   |

| t <sub>F</sub>     | Fall Time <sup>[2]</sup><br>VT = 20% to 80% of swing |                                                                                                                           | 120 | 325 | 595  | ps   |

| t <sub>DC</sub>    | Output Duty Cycle [6]                                | Across all settings in this table, $V_T = 0V$ .                                                                           | 48  | 50  | 52   | %    |

1. Standard high impedance load with CL= 2pF. For more information, see Test Loads.

2. Measured from single-ended waveform.

3. Measured at crossing point where the instantaneous voltage value of the rising edge of CLK equals the falling edge of CLKb.

4. Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossing points for this measurement.

5. Defined as the total variation of all crossing voltages of Rising CLK and Falling CLKb. This is the maximum allowed variance in VCROSS for any particular system.

6. Measured from differential waveform.

| Symbol             | Parameter                                 | Condition                                                                                                                                                                                | MIN | ТҮР | МАХ | Unit |

|--------------------|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| V <sub>OH</sub>    | Output High Voltage [2]                   |                                                                                                                                                                                          | 360 | 395 | 430 |      |

| V <sub>OL</sub>    | Output Low Voltage [2]                    |                                                                                                                                                                                          | -25 | 8   | 45  |      |

| V <sub>CROSS</sub> | Crossing Voltage (abs) [3]                | VHIGH = 800mV, Fast Slew Rate,<br>156.25MHz, 312.5MHz - amplitude is<br>reduced by ~50% due to double<br>termination. (Slow slew rate is not<br>recommended for frequencies ><br>100MHz) | 150 | 185 | 215 | mV   |

| $\Delta V_{CROSS}$ | Crossing Voltage (var) [3][4][5]          |                                                                                                                                                                                          | -12 | 10  | 30  |      |

| t <sub>R</sub>     | Rise Time [2]<br>VT = 20% to 80% of swing |                                                                                                                                                                                          | 150 | 310 | 557 | ps   |

| t <sub>F</sub>     | Fall Time [2]<br>VT = 20% to 80% of swing |                                                                                                                                                                                          | 110 | 260 | 380 | ps   |

| V <sub>OH</sub>    | Output High Voltage [2]                   |                                                                                                                                                                                          | 380 | 480 | 560 |      |

| V <sub>OL</sub>    | Output Low Voltage [2]                    | _                                                                                                                                                                                        | -30 | 10  | 50  | .,   |

| V <sub>CROSS</sub> | Crossing Voltage (abs) [3]                | Vніgн = 900mV, Fast Slew Rate,                                                                                                                                                           | 165 | 220 | 280 | mV   |

| $\Delta V_{CROSS}$ | Crossing Voltage (var) [3][4][5]          | <ul> <li>156.25MHz, 312.5MHz - amplitude is<br/>reduced by ~50% due to double</li> </ul>                                                                                                 | -18 | 10  | 30  |      |

| t <sub>R</sub>     | Rise Time [2]<br>VT = 20% to 80% of swing | termination. (Slow slew rate is not<br>recommended for<br>frequencies >100MHz)                                                                                                           | 170 | 320 | 610 | ps   |

| t <sub>F</sub>     | Fall Time [2]<br>VT = 20% to 80% of swing |                                                                                                                                                                                          | 130 | 305 | 400 | ps   |

| t <sub>DC</sub>    | Output Duty Cycle [6]                     | Across all settings in this table, VT = 0V.                                                                                                                                              | 48  | 50  | 52  | %    |

#### Table 11. RS2CB19008A 100Ω CLK AC/DC Characteristics–Non-PCIe Apps, Double-Terminated Loads <sup>[1]</sup>

1. Both Tx and Rx are terminated (double-terminated) with C<sub>L</sub>= 2pF. This reduces amplitude by 50%. For more information, see Test Loads.

2. Measured from single-ended waveform.

3. Measured at crossing point where the instantaneous voltage value of the rising edge of CLK equals the falling edge of CLKb.

4. Refers to the total variation from the lowest crossing point to the highest, regardless of which edge is crossing. Refers to all crossing points for this measurement.

5. Defined as the total variation of all crossing voltages of Rising CLK and Falling CLKb. This is the maximum allowed variance in VCROSS for any particular system.

6. Measured from differential waveform.

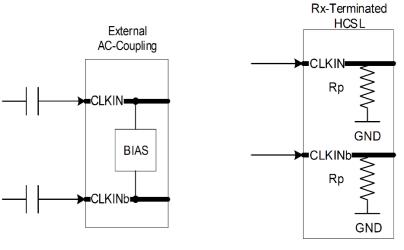

## 2.5.4 CLKIN AC/DC Characteristics

#### Table 12. CLKIN AC/DC Characteristic

| Symbol             | Parameter               | Condition                               | <b>MIN</b> [1] | ТҮР | MAX  | Unit |

|--------------------|-------------------------|-----------------------------------------|----------------|-----|------|------|

| V <sub>CROSS</sub> | Input Crossover Voltage | -                                       | 100            | -   | 1400 | mV   |

| V <sub>SWING</sub> | Input Swing             | Differential value.                     | 200            | -   | -    | mV   |

| dv/dt              | Input Slew Rate         | Measured differentially. <sup>[2]</sup> | 0.6            | -   | -    | V/ns |

1. For values required for performance, see the Phase Jitter tables.

2. Measured from -150mV to +150mV on the differential waveform (derived from REFCLK+ minus REFCLK-). The signal must be monotonic through the measurement region for rise and fall time. The 300mV measurement window is centered on the differential zero-crossing.

### 2.5.5 Output-to-Output and Input-to-Output Skew

#### Table 13. RS2CB19008A Output-to-Output and Input-to-Output Skew<sup>[1]</sup>

| Symbol          | Parameter             | Condition                                              | MIN | ТҮР | МАХ | Unit |

|-----------------|-----------------------|--------------------------------------------------------|-----|-----|-----|------|

| t               | Output-to-Output Skew | Any two outputs, all outputs at fast slew rate.        | -   | 38  | 50  | ps   |

| t <sub>SK</sub> | [2]                   | Any two outputs, all outputs at slow slew rate.        | -   | 40  | 60  | ps   |

|                 | Input-to-Output Delay | Clock in to any output, all outputs at fast slew rate. | 1.1 | 1.2 | 1.4 | ns   |

### RS2CB19008A Series Clock Buffer

PCIe Gen5/6 1:8 Fan out Buffer with LOS

| t <sub>PD</sub>           | Double-Terminated [3]                             | Clock in to any output, all outputs at slow slew rate. | 1.2 | 1.4 | 1.6 | ns    |

|---------------------------|---------------------------------------------------|--------------------------------------------------------|-----|-----|-----|-------|

| taa Input-to-Output Delay |                                                   | Clock in to any output, all outputs at fast slew rate. | 1.2 | 1.4 | 1.6 | ns    |

| t <sub>PD</sub>           | Source-Terminated <sup>[3]</sup>                  | Clock in to any output, all outputs at slow slew rate. | 1.4 | 1.5 | 1.8 | ns    |

| $\Delta t_{PD}$           | Input-to-Output Delay<br>Variation <sup>[3]</sup> | A single device, over temperature and voltage.         | -   | 1.4 | 2   | ps/°C |

1. For more information, see Test Loads.

2. This parameter is defined in accordance with JEDEC Standard 65.

3. Defined as the time between to output rising edge and the input rising edge that caused it.

### 2.5.6 I/O Signals

| Table 14. I | /O Electrical | Characteristics |

|-------------|---------------|-----------------|

|-------------|---------------|-----------------|

| Symbol | Parameter                                | Condition                                                 | MIN  | ТҮР | MAX          | Unit |

|--------|------------------------------------------|-----------------------------------------------------------|------|-----|--------------|------|

| Viн    | Input High Voltage [1][2]                | Single-ended inputs, unless otherwise                     | 2    | -   | VDD +<br>0.3 | V    |

| VIL    | Input Low Voltage [1][2]                 | listed.                                                   | -0.3 | -   | 0.8          | V    |

| Vih    | Input High Voltage                       |                                                           | 2.4  | -   | VDD+0.3      | V    |

| Vim    | Input Mid Voltage                        | SADR_tri[1:0].                                            | 1.2  | -   | 1.8          | V    |