#### **Features**

- PCle Gen5 Phase Jitter < 80fs rms

- 3.3V operation voltage

- 85Ω differential Low-Power HCSL (LP-HCSL) outputs eliminate 32 resistors

- selectable SMBus addresses

- Supports 0%, -0.3% and -0.5% spreadspectrum amounts

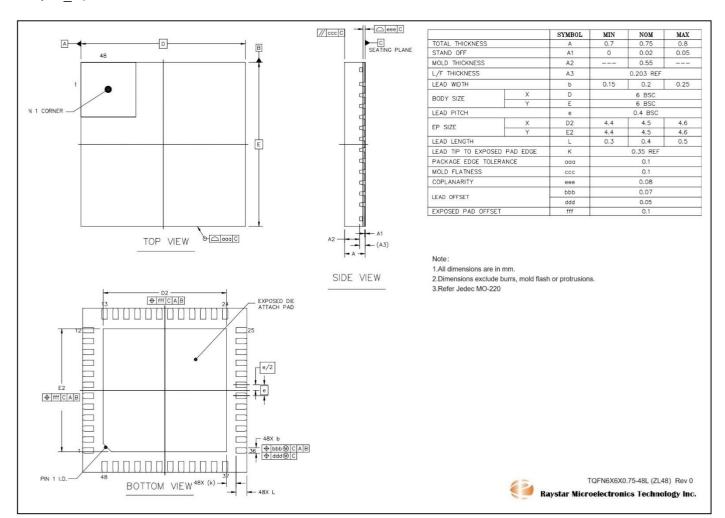

- 6 mm x 6 mm TQFN-48L

#### **Output Features**

- 1 25MHz output pairs

- 6 100MHz output pairs

- 2 MXCLK output pairs multiplexable between 100MHz and 25MHz

- Dedicated Platform Time Input clock

### **Application**

- Cloud/High-performance Computing

- nVME Storage

- Networking

- PCIe switch

### **Description**

The RS2CG2008 is a single-chip, PCIe Gen5 clock synthesizer. It is designed to work as a complete clock solution which matches PCIe Gen5 specification or in combination with DB2000QL-compliant clock buffers. It is part of the next generation clock generator family supporting the latest dual and multi-socket Intel server platforms.

#### **PCIe Clocking Architecture**

- Common Clocked (CC)

- Independent Reference (IR) with and without spread spectrum

### **Ordering Information**

| Part Number  | Package  | Description                 |

|--------------|----------|-----------------------------|

| RS2CG2008ZLE | TQFN_48L | 6 x 6 x 0.75 mm,0.4mm Pitch |

#### Notes:

1

[1] E = Pb-free and Green

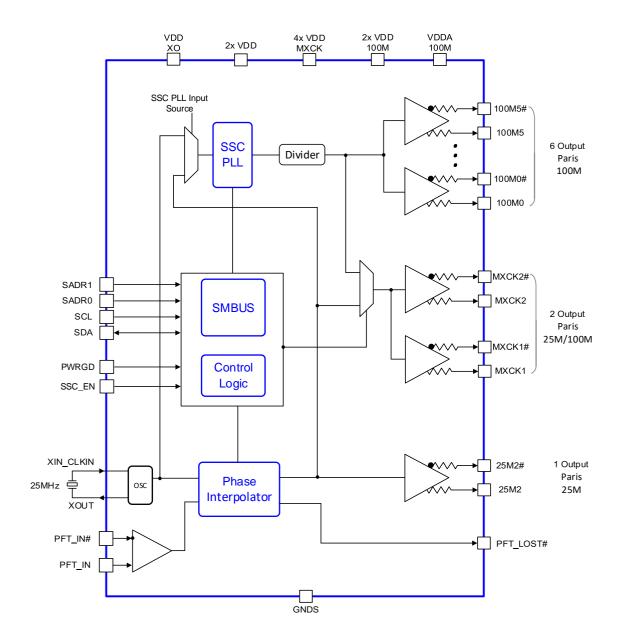

# **Block Diagram**

## **Pin Configuration**

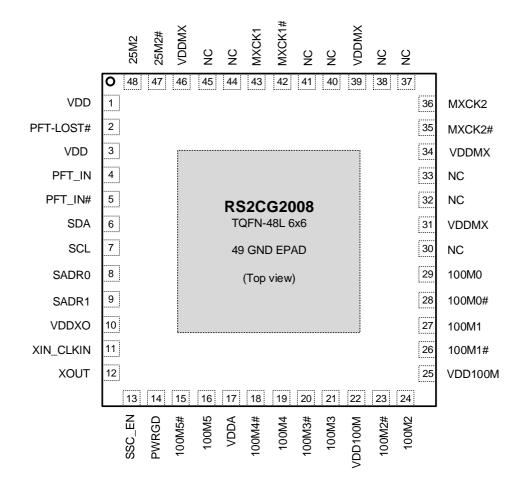

Figure 1. Pin Assignments for 6×6 mm TQFN-48L Package – Top View

### **Top Marking**

RS2CG2008ZLE—Part Number AYYWWJK—Production Tracing Code

# **Pin Description**

**Table 1. Pin Descriptions**

| Pin Name  | Number | Туре          | Description                                                                                                                                         |

|-----------|--------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 100M0     | 29     | O, DIF        | ±0.7V LP-HCSL differential 100MHz clock true output.                                                                                                |

| 100M0#    | 28     | O, DIF        | ±0.7V LP-HCSL differential 100MHz clock complement output.                                                                                          |

| 100M1     | 27     | O, DIF        | ±0.7V LP-HCSL differential 100MHz clock true output.                                                                                                |

| 100M1#    | 26     | O, DIF        | ±0.7V LP-HCSL differential 100MHz clock complement output.                                                                                          |

| 100M2     | 24     | O, DIF        | ±0.7V LP-HCSL differential 100MHz clock true output.                                                                                                |

| 100M2#    | 23     | O, DIF        | ±0.7V LP-HCSL differential 100MHz clock complement output.                                                                                          |

| 100M3     | 21     | O, DIF        | ±0.7V LP-HCSL differential 100MHz clock true output.                                                                                                |

| 100M3#    | 20     | O, DIF        | ±0.7V LP-HCSL differential 100MHz clock complement output.                                                                                          |

| 100M4     | 19     | O, DIF        | ±0.7V LP-HCSL differential 100MHz clock true output.                                                                                                |

| 100M4#    | 18     | O, DIF        | ±0.7V LP-HCSL differential 100MHz clock complement output.                                                                                          |

| 100M5     | 16     | O, DIF        | ±0.7V LP-HCSL differential 100MHz clock true output.                                                                                                |

| 100M5#    | 15     | O, DIF        | ±0.7V LP-HCSL differential 100MHz clock complement output.                                                                                          |

| 25M2      | 48     | O, DIF        | ±0.7V LP-HCSL differential 25MHz true output.                                                                                                       |

| 25M2#     | 47     | O, DIF        | ±0.7V LP-HCSL differential 25MHz complement output.                                                                                                 |

| GND       | 49     | GND           | GND EPAD.                                                                                                                                           |

| MXCK1     | 43     | O, DIF        | ±0.7V LP-HCSL differential multiplexable clock true output.                                                                                         |

| MXCK1#    | 42     | O, DIF        | ±0.7V LP-HCSL differential multiplexable clock complement output.                                                                                   |

| MXCK2     | 36     | O, DIF        | ±0.7V LP-HCSL differential multiplexable clock true output.                                                                                         |

| MXCK2#    | 35     | O, DIF        | ±0.7V LP-HCSL differential multiplexable clock complement output.                                                                                   |

| NC        | 45     | _             | No connection.                                                                                                                                      |

| NC        | 44     | _             | No connection.                                                                                                                                      |

| NC        | 41     | _             | No connection.                                                                                                                                      |

| NC        | 40     | _             | No connection.                                                                                                                                      |

| NC        | 38     | _             | No connection.                                                                                                                                      |

| NC        | 37     | _             | No connection.                                                                                                                                      |

| NC        | 33     | _             | No connection.                                                                                                                                      |

| NC        | 32     |               | No connection.                                                                                                                                      |

| NC        | 30     | _             | No connection.                                                                                                                                      |

| PFT_IN    | 4      | I, DIF, PDT   | ±0.7V 25MHz differential platform time input.                                                                                                       |

| PFT_IN#   | 5      | I, DIF, PDT   | ±0.7V 25MHz differential platform time input.                                                                                                       |

| PFT_LOST# | 2      | OD, SE        | Asserts when PFT_IN, PFT_IN# clock is not present.                                                                                                  |

| PWRGD     | 14     | I, SE, PU     | 3.3V LVTTL input to power up or power down the device.                                                                                              |

| SADR0     | 8      | I, SE, PD, PU | 3.3V tri-level LVTTL input to select SMBus address. Refer to tri-level input threshold table.                                                       |

| SADR1     | 9      | I, SE, PD, PU | 3.3V tri-level LVTTL input to select SMBus address. Refer to tri-level input threshold table.                                                       |

| SDA       | 6      | IO, OD, PDT   | Open drain bi-directional SMBus data.                                                                                                               |

| SCL       | 7      | I, SE, PDT    | SMBus slave clock input.                                                                                                                            |

| SSC_EN    | 13     | I, SE, PD     | Tri-level input to enable or disable spread spectrum. Refer to tri-level input threshold table. 0 = SSC off, MID = -0.3% max, and HIGH = -0.5% max. |

| VDD100M   | 22     | Power         | Power supply for 100M outputs.                                                                                                                      |

| VDD100M   | 25     | Power         | Power supply for 100M outputs.                                                                                                                      |

| VDDA      | 17     | Power         | Analog power supply for 100M outputs.                                                                                                               |

| VDDMX     | 46     | Power         | Power supply for MXCK outputs.                                                                                                                      |

| Pin Name  | Number | Туре       | Description                                                                                               |

|-----------|--------|------------|-----------------------------------------------------------------------------------------------------------|

| VDDMX     | 39     | Power      | Power supply for MXCK outputs.                                                                            |

| VDDMX     | 34     | Power      | Power supply for MXCK outputs.                                                                            |

| VDDMX     | 31     | Power      | Power supply for MXCK outputs.                                                                            |

| VDD       | 1      | Power      | Power supply for 25M outputs and platform time circuit and digital.                                       |

| VDD       | 3      | Power      | Power supply for 25M outputs and platform time circuit and digital.                                       |

| VDDXO     | 10     | Power      | Power supply for internal crystal oscillator.                                                             |

| XIN_CLKIN | 11     | I, SE, PDT | Crystal input / Single-ended input.                                                                       |

| XOUT      | 12     | O, SE      | Output of internal crystal oscillator. This pin should be left floating if CLK_IN function is being used. |

Table 2. Signal Types

| Term  | Description                                                                                    |

|-------|------------------------------------------------------------------------------------------------|

| I     | Input                                                                                          |

| 0     | Output                                                                                         |

| OD    | Open Drain Output                                                                              |

| I/O   | Bi-Directional                                                                                 |

| PD    | Pull-down                                                                                      |

| PU    | Pull-up                                                                                        |

| Z     | Tristate                                                                                       |

| D     | Driven                                                                                         |

| Х     | Don't care                                                                                     |

| SE    | Single-ended                                                                                   |

| DIF   | Differential                                                                                   |

| Power | 3.3V power                                                                                     |

| GND   | Ground                                                                                         |

| PDT   | Power Down Tolerant: These signals must tolerate being driven when the device is powered down. |

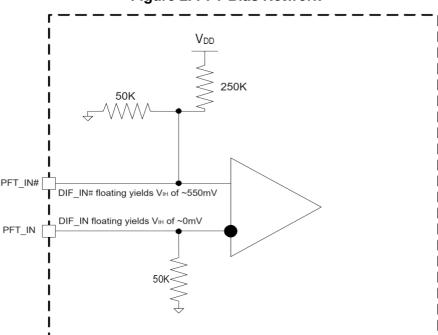

### **Platform Time Input**

The RS2CG2008 support a dedicated Platform Time Input clock. These pins receive clock from another clock device to keep synchronization across servers. PFT\_IN allows different devices to frequency lock the 25 MHz clocks to a single time base. The local 25 MHz frequency locks to the PFT\_IN clock if it is present. If PFT\_IN is not present, the local 25MHz frequency is sourced from the local crystal.

6

Figure 2. PFT Bias Network

### **Output Enable Control**

The outputs of RS2CG2008 is controlled by using the SMBus output enable bits. Any of the 9 outputs have dedicated SMBus output enable bits in Bytes[0:2] of the SMBus register set that can enable or disable the clock outputs. The Output Enable bits in the SMBus registers are active high and are set to enable by default.

Table 3. OE Functionality for 100M [5:0] Outputs

| PWRGD | SMBus OE Bit | 100M [5:0] |

|-------|--------------|------------|

| 0     | X            | Disabled   |

| 1     | 0            | Disabled   |

| ı     | 1            | Running    |

Note: Disabled in this table means both the true and complement output are low.

Table 4. OE Functionality for 25M [2] and MXCK [2:1] Outputs

| PWRGD | SMBus OE Bit | MXCK [2:1] | 25M [2]  |

|-------|--------------|------------|----------|

| 0     | X            | Disabled   | Disabled |

| 1     | 0            | Disabled   | Disabled |

|       | 1            | Running    | Running  |

Note: Disabled in this table means both the true and complement output are low.

7

### **Absolute Maximum Ratings**

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the RS2CG2008 at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

**Table 5. Absolute Maximum Ratings**

| Parameter               | Symbol           | Conditions                              | MIN  | TYP | MAX | Units | Notes |

|-------------------------|------------------|-----------------------------------------|------|-----|-----|-------|-------|

| Supply Voltage          | V <sub>DDX</sub> |                                         |      |     | 3.9 | V     | 1     |

| 3.3V Input High Voltage | V <sub>IH</sub>  |                                         |      |     | 3.9 | V     | 2     |

| 3.3V Input Low Voltage  | V <sub>IL</sub>  |                                         | -0.5 |     |     | V     |       |

| Storage Temperature     | TS               |                                         | -65  |     | 150 | °C    |       |

| Junction Temperature    | TJ               | Maximum operating junction temperature. |      |     | 125 | °C    |       |

| Input ESD Protection    | ESD              | Human Body Model.                       | 2000 |     |     | V     |       |

<sup>1.</sup> Operation over these conditions is neither implied nor guaranteed.

<sup>2.</sup> Maximum VIH is not to exceed maximum VDD.

#### **Electrical Characteristics**

TA = TAMB. Supply voltages per normal operation conditions; see Test Loads for loading conditions.

#### **Table 6. AC Characteristics for SMBus**

| Parameter                                                       | Symbol               | 100K | Class | Specifica<br>Limits 10 | ation<br>00K Class | 400K | Class | Specification<br>Limits 400K Class |     | Units | Notes |

|-----------------------------------------------------------------|----------------------|------|-------|------------------------|--------------------|------|-------|------------------------------------|-----|-------|-------|

|                                                                 |                      | MIN  | MAX   | MIN                    | MAX                | MIN  | MAX   | MIN                                | MAX |       |       |

| SMBus Operating<br>Frequency                                    | f <sub>SMB</sub>     | 10   | 100   | 10                     | 100                | 10   | 400   | 10                                 | 400 | kHz   |       |

| Bus Free Time<br>between STOP and<br>START Condition            | t <sub>BUF</sub>     | 4.7  | _     | 4.7                    | _                  | 1.3  | _     | 1.3                                | _   | μs    |       |

| Hold Time after (REPEATED) START Condition                      | <sup>t</sup> HD:STA  | 4    | _     | 4                      | _                  | 0.6  | 1     | 0.6                                | _   | μs    | 1     |

| REPEATED START Condition Setup Time                             | <sup>t</sup> SU:STA  | 4.7  | _     | 4.7                    | _                  | 0.6  | _     | 0.6                                | _   | μs    |       |

| STOP Condition Setup<br>Time                                    | t <sub>SU:STO</sub>  | 4    | _     | 4                      | _                  | 0.6  | 1     | 0.6                                | _   | μs    |       |

| Data Hold Time                                                  | tHD:DAT              | 300  | _     | 300                    | _                  | 300  | _     | 0                                  | _   | ns    | 2     |

| Data Setup Time                                                 | tSU:DAT              | 250  | _     | 250                    | _                  | 100  | _     | 100                                | _   | ns    |       |

| Detect SMBDAT Low<br>Timeout                                    | <sup>t</sup> TIMEOUT | 25   | 35    | 25                     | 35                 | 25   | 35    | 25                                 | 35  | ms    | 3     |

| Detect Clock Low<br>Timeout                                     | <sup>t</sup> TIMEOUT | 25   | 35    | 25                     | 35                 | 25   | 35    | 25                                 | 35  | ms    | 4     |

| Clock Low Period                                                | tLOW                 | 4.7  | _     | 4.7                    | _                  | 1.3  | _     | 1.3                                | _   | μs    |       |

| Clock High Period                                               | t <sub>HIGH</sub>    | 4    | 50    | 4                      | 50                 | 0.6  | 50    | 0.6                                | 50  | μs    | 5     |

| Clock/Data Fall Time                                            | t <sub>F</sub>       | _    | 300   | _                      | 300                | _    | 300   | _                                  | 300 | ns    | 6     |

| Clock/Data Rise Time                                            | t <sub>R</sub>       | _    | 1000  | _                      | 1000               | _    | 300   | _                                  | 300 | ns    | 6     |

| Time in which a device must be operational after power-on reset | <sup>t</sup> POR     |      | 5     |                        | 500                |      | 5     |                                    | 500 | ms    | 7     |

<sup>&</sup>lt;sup>1</sup> After this period, the first clock is generated.

9

<sup>&</sup>lt;sup>2</sup> The RS2CG2008 device maintains 300ns data hold time for backwards compatibility with the SMBus 2.0 specification. Newer versions of the SMBus specification call out 0ns data hold time for both 100kHz and 400kHz classes.

$<sup>^3</sup>$  The RS2CG2008 provided additional SMBus protection by implementing a timeout for SDA being held low in excess of  $t_{\text{TIMEOUT}}$ , in addition to the SCLK low timeout.

<sup>&</sup>lt;sup>4</sup> Devices participating in a transfer can abort the transfer in progress and release the bus when any single clock low interval exceeds the value of total transfer can abort the master in a transaction detects this condition, it must generate a stop condition within or after the current data byte in the transfer process. Devices that have detected this condition must reset their communication and be able to receive a new START condition no later than total transfer the SMBus. Some simple device examples include the host controller, and embedded controller, and most devices that can master the SMBus. Some simple devices do not contain a clock low drive circuit; this simple kind of device typically may reset its communications port after a start or a stop condition. A timeout condition can only be ensured if the device that is forcing the timeout holds the SMBCLK low for total transfer in progress and release the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds the bus when any single clock low interval exceeds t

<sup>&</sup>lt;sup>5</sup> t<sub>HIGH</sub>, Maximum provides a simple guaranteed method for masters to detect bus idle conditions. A master can assume that the bus is free if it detects that the clock and data signals have been high for greater than t<sub>HIGH</sub>, Maximum.

<sup>&</sup>lt;sup>6</sup> The rise and fall time measurement limits are defined as follows: Rise Time Limits: (VIL, MAX - 0.15V) to (VIH,MIN + 0.15V) Fall Time Limits: (VIH,MIN + 0.15 V) to (VIL,MAX - 0.15V)

<sup>&</sup>lt;sup>7</sup> Power must be applied and PWRGD must be a 1 for the SMBus to be active.

### Table 7. DC Characteristics for Input/Supply/Common

| Parameter                        | Symbol                           | Conditions                                                                                                                                                         | MIN       | TYP                | MAX                   | Units | Notes |

|----------------------------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------|-----------------------|-------|-------|

| Supply Voltage                   | V <sub>DDX</sub>                 | 3.3V ±5%.                                                                                                                                                          | 3.135     | 3.3                | 3.465                 | V     |       |

| Ambient Operating<br>Temperature | T <sub>AMB</sub>                 | No airflow.                                                                                                                                                        | -40       | 25                 | 85                    | °C    |       |

| Input High Voltage               | VIH                              | Single-ended inputs, except SMBus, and tri-<br>level inputs.                                                                                                       | 2         |                    | V <sub>DD</sub> + 0.3 | V     |       |

| Input Low Voltage                | V <sub>IL</sub>                  | Single-ended inputs, except SMBus, and trilevel inputs.                                                                                                            | GND - 0.3 |                    | 0.8                   | V     |       |

| Input High Voltage               | V <sub>IH</sub>                  | Tri-level inputs.                                                                                                                                                  | 2.5       |                    | V <sub>DD</sub> + 0.3 | ٧     |       |

| Input Mid Voltage                | $v_{IM}$                         | Tri-level inputs.                                                                                                                                                  | 1.2       | V <sub>DD</sub> /2 | 1.8                   | ٧     |       |

| Input Low Voltage                | V <sub>IL</sub>                  | Tri-level inputs.                                                                                                                                                  | GND - 0.3 |                    | 0.8                   | ٧     |       |

|                                  | I <sub>IN</sub>                  | Single-ended inputs, $V_{IN} = GND$ , $V_{IN} = V_{DD}$ .                                                                                                          | -5        |                    | 5                     | μΑ    |       |

| Input Current                    | IINPUPD                          | Single-ended inputs.  V <sub>IN</sub> = 0 V; Inputs with internal pull-up resistors. V <sub>IN</sub> = V <sub>DD</sub> ; Inputs with internal pull-down resistors. | -50       | ±40                | 50                    | μА    |       |

|                                  | P <sub>UP</sub> /P <sub>DN</sub> | Value of internal pull-up and pull-down resistors, except PFT_IN/PFT_IN#.                                                                                          |           | 120                |                       | kΩ    |       |

| Internal Resistor<br>Values      | P <sub>DN_PFT_IN/#</sub>         | Value of internal pull-down resistor on PFT_IN or PFT_IN#.                                                                                                         |           | 50                 |                       | kΩ    |       |

|                                  | P <sub>UP</sub> PFT_IN#          | Value of internal pull-up resistor to 0.55V on PFT_IN#.                                                                                                            |           | 250                |                       | kΩ    |       |

| Input Frequency                  | F <sub>IN</sub>                  |                                                                                                                                                                    |           | 50                 |                       | MHz   |       |

| Pin Inductance                   | L <sub>pin</sub>                 |                                                                                                                                                                    |           |                    | 7                     | nΗ    | 1     |

|                                  | C <sub>IN</sub>                  | Logic inputs, except DIF_IN.                                                                                                                                       |           |                    | 4.5                   | pF    | 1     |

| Capacitance                      | C <sub>INDIF_IN</sub>            | Differential clock inputs.                                                                                                                                         |           |                    | 2.7                   | pF    | 1     |

| ·                                | C <sub>OUT</sub>                 | Output pin capacitance.                                                                                                                                            |           |                    | 4.5                   | pF    | 1     |

| Clk Stabilization                | T <sub>STAB</sub>                | From V <sub>DD</sub> power-up and after input clock stabilization or de-assertion of PWRDN# to                                                                     |           |                    | 5                     | ms    | 1,2   |

| Tdrive_PD#                       | <sup>t</sup> DRVPD               | Differential output enable after PWRDN# deassertion.                                                                                                               |           |                    | 300                   | μs    | 1,3   |

| Tfall                            | tF                               | Fall time of control inputs.                                                                                                                                       |           |                    | 5                     | ns    | 2     |

| Trise                            | t <sub>R</sub>                   | Rise time of control inputs.                                                                                                                                       |           |                    | 5                     | ns    | 2     |

10

$<sup>^{\</sup>rm 1}$  Guaranteed by design and characterization, not 100% tested in production.

<sup>&</sup>lt;sup>2</sup> Control input must be monotonic from 20% to 80% of input swing.

<sup>&</sup>lt;sup>3</sup> Refers to device differential input clock.

#### Table 9. Skew, Jitter and Duty Cycle

T<sub>AMB</sub> = over the specified range. Supply voltages per normal operation conditions; see Test Loads for loading conditions.

| Parameter                                  | Symbol                   | Conditions                                                                             | MIN | TYP | MAX | Specification<br>Limit | Units | Notes |

|--------------------------------------------|--------------------------|----------------------------------------------------------------------------------------|-----|-----|-----|------------------------|-------|-------|

| Output to Output<br>Skew within a<br>Group | <sup>t</sup> SKEWGRP     | Groups are 25M[2], MXCK[2:1], and 100M[5:0].                                           |     | 100 |     | TBD                    | ps    | 1,2   |

| Output to Output<br>Skew Across<br>Groups  | <sup>t</sup> SKEWGRP2GRP | Across 25M[2] and MXCK[2:1] set to 25MHz or 100M[5:0] and MXCK[2:1] set to 100MHz.     |     | 0.5 |     | 1                      | ns    | 1,2   |

| Cycle to Cycle Jitter                      | t <sub>JCC25</sub>       | 25MHz Outputs and MXCLK outputs set to 25MHz.                                          |     | 0.5 |     | 1                      | ns    | 1,2   |

| Cycle to Cycle ditter                      | <sup>t</sup> JCC100      | 100MHz Outputs and MXCLK outputs set to 100MHz.                                        |     | 25  |     | 1                      | ps    | 1,2   |

|                                            | <sup>t</sup> DC100       | 100MHz Outputs and MXCLK outputs set to 100MHz.                                        | 45  | 50  | 55  | 1                      | %     | 1,2   |

| Duty Cycle                                 | t <sub>DC25</sub>        | 25MHz Outputs and MXCLK outputs set to 25MHz with XTAL as source.                      | 45  | 50  | 55  | 1                      | ps    | 1,2   |

|                                            | t <sub>DC25</sub>        | 25MHz Outputs and MXCLK outputs set to 25MHz with XO as source with 44/55% duty cycle. | 43  | 50  | 57  | 1                      | ps    | 1,2   |

<sup>&</sup>lt;sup>1</sup> Measured into AC test load.

#### Table 10. PCle Phase Jitter

TAMB = over the specified range. Supply voltages per normal operation conditions; see Test Loads for loading conditions.

| Parameter                                | Symbol                      | Conditions                   | MIN | TYP  | MAX | Limit | Units    | Notes   |

|------------------------------------------|-----------------------------|------------------------------|-----|------|-----|-------|----------|---------|

|                                          | <sup>t</sup> jphPCleG1-CC   | PCIe Gen1 (2.5 GT/s)         |     | 20   |     | 86    | ps (p-p) | 1,2     |

|                                          | t: 1 pol 00 00              | PCIe Gen2 Hi Band (5.0 GT/s) |     | 0.70 |     | 3     | ps (RMS) | 1,2     |

| PCIe Phase Jitter                        | <sup>t</sup> jphPCleG2-CC   | PCIe Gen2 Lo Band (5.0 GT/s) |     | 0.50 |     | 3.1   | ps (RMS) | 1,2     |

| (Common Clocked<br>Architecture)         | tjphPCleG3-CC               | PCle Gen3 (8.0 GT/s)         |     | 0.20 |     | 1     | ps (RMS) | 1,2,3   |

|                                          | <sup>t</sup> jphPCleG4-CC   | PCIe Gen4 (16.0 GT/s)        |     | 0.20 |     | 0.4   | ps (RMS) | 1,2,3,4 |

|                                          | <sup>t</sup> jphPCleG5-CC   | PCIe Gen5 (32.0 GT/s)        |     | 0.04 |     | 0.08  | ps (RMS) | 1,2,3,5 |

|                                          | <sup>t</sup> jphPCleG1-SRIS | PCIe Gen1 (2.5 GT/s)         |     | 10   |     |       | ps (RMS) | 1,2,6   |

|                                          | <sup>t</sup> jphPCleG2-SRIS | PCle Gen2 (5.0 GT/s)         |     | 0.50 |     |       | ps (RMS) | 1,2,6   |

| PCIe Phase Jitter<br>(SRIS Architecture) | tjphPCleG3-SRIS             | PCle Gen3 (8.0 GT/s)         |     | 0.25 |     | N/A   | ps (RMS) | 1,2,6   |

| ,                                        | <sup>t</sup> jphPCleG4-SRIS | PCIe Gen4 (16.0 GT/s)        |     | 0.26 |     |       | ps (RMS) | 1,2,6   |

|                                          | <sup>t</sup> jphPCleG5-SRIS | PCIe Gen5 (32.0 GT/s)        |     | 0.05 |     |       | ps (RMS) | 1,2,6   |

<sup>&</sup>lt;sup>1</sup> The Refclk jitter is measured after applying the filter functions found in PCI Express Base Specification 5.0, Revision 1.0. See the Test Loads section of the data sheet for the exact measurement setup. Values for the Common Clock architecture are calculated with spread off and spread on at <-0.5%. SRIS values are calculated for spread off and spread on at ≤ -0.3%. The worst case results for each data rate are summarized in this table. If oscilloscope data is used, equipment noise is removed from all results. See Test Load for PCIe Phase Jitter Measurements.

<sup>&</sup>lt;sup>2</sup> Measured from differential cross-point to differential cross-point.

- <sup>2</sup> Jitter measurements shall be made with a capture of at least 100,000 clock cycles captured by a real-time oscilloscope (RTO) with a sample rate of 20 GS/s or greater. Broadband oscilloscope noise must be minimized in the measurement. The measured PP jitter is used (no extrapolation) for RTO measurements. Alternately Jitter measurements may be made with a Phase Noise Analyzer (PNA) extending (flat) and integrating and folding the frequency content up to an offset from the carrier frequency of at least 200MHz (at 300MHz absolute frequency) below the Nyquist frequency. For PNA measurements for the 2.5GT/s data rate, the RMS jitter is converted to peak to peak jitter using a multiplication factor of 8.83. In the case where real-time oscilloscope and PNA measurements have both been done and produce different results, the RTO result must be used.

- <sup>3</sup> SSC spurs from the fundamental and harmonics are removed up to a cutoff frequency of 2 MHz taking care to minimize removal of any non-SSC content.

- <sup>4</sup> Note that 0.7ps RMS is to be used in channel simulations to account for additional noise in a real system.

- <sup>5</sup> Note that 0.25ps RMS is to be used in channel simulations to account for additional noise in a real system.

- <sup>6</sup> The PCI Express Base Specification 5.0, Revision 1.0 provides the filters necessary to calculate SRIS jitter values, however, it does not provide specification limits, hence the n/a in the Limit column. SRIS values are informative only. In general, a clock operating in an SRIS system must be twice as good as a clock operating in a Common Clock system. For RMS values, twice as good is equivalent to dividing the CC value by √2. And additional consideration is the value for which to divide by √2. The conservative approach is to divide the ref clock jitter limit, and the case can be made for dividing the channel simulation values by √2, if the ref clock is close to the Tx clock input. An example for Gen4 is as follows. A "rule-of-thumb" SRIS limit would be either 0.5ps RMS/√2 = 0.35ps RMS if the clock chip is far from the clock input, or 0.7ps RMS/√2 = 0.5ps RMS if the clock chip is near the clock input.

#### Table 11. Differential Clock Outputs Driving High Impedance Receiver

TAMB = over the specified range. Supply voltages per normal operation conditions; see Test Loads for loading conditions.

| Parameter              | Symbol     | Conditions                                               | MIN | TYP | MAX | Specification<br>Limit | Units | Notes   |

|------------------------|------------|----------------------------------------------------------|-----|-----|-----|------------------------|-------|---------|

| Slew Rate              | dV/dt      | Scope averaging on, fast setting.                        | 2   | 3   |     | 2 – 4                  | V/ns  | 1,2,3   |

| Slew Rate Matching     | ΔdV/dt     | Single-ended measurement.                                |     | 0   |     | 20                     | %     | 1       |

| Maximum Voltage        | Vmax       | Measurement on single-ended signal using absolute value. |     | 800 |     | 1150                   | mV    | 1,7,8   |

| Minimum Voltage        | Vmin       | (scope averaging off).                                   |     | 0   |     | -300 to +150           |       | 1,5,7,8 |

| Crossing Voltage (abs) | Vcross_abs | Scope averaging off.                                     |     | 400 |     | 250 – 550              | mV    | 1,6,7   |

| Crossing Voltage (var) | Δ-Vcross   | Scope averaging off.                                     |     | 0   |     | 140                    | mV    | 1,6,7   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

12

<sup>&</sup>lt;sup>2</sup> Measured from differential waveform.

<sup>&</sup>lt;sup>3</sup> Slew rate is measured through the Vswing voltage range centered around differential 0 V. This results in a ±150mV window around differential 0V.

<sup>&</sup>lt;sup>4</sup> Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a ±75mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations.

<sup>&</sup>lt;sup>5</sup> Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock\_rising and Clock# falling).

<sup>&</sup>lt;sup>6</sup> The total variation of all Vcross measurements in any particular system. Note that this is a subset of Vcross\_min/max (Vcross absolute) allowed. The intent is to limit Vcross induced modulation by setting Δ-Vcross to be smaller than Vcross absolute.

<sup>&</sup>lt;sup>7</sup> At default SMBus settings.

<sup>&</sup>lt;sup>8</sup> Includes 300mV of overshoot for Vmax and 300mV of undershoot for Vmin.

### **Table 12. Differential Clock Outputs Driving Terminated Receiver (Double Termination)**

TAMB = over the specified range. Supply voltages per normal operation conditions; see Test Loads for loading conditions.

| Parameter              | Symbol     | Conditions                                               | MIN | TYP | MAX | Specification<br>Limit | Units | Notes   |

|------------------------|------------|----------------------------------------------------------|-----|-----|-----|------------------------|-------|---------|

| Slew Rate              | dV/dt      | Scope averaging on, fast setting.                        | 1   | 2   |     | 1 – 3                  | V/ns  | 1,2,3   |

| Slew Rate Matching     | ∆dV/dt     | Single-ended measurement.                                |     | 0   | 20  | 20                     | %     |         |

| Maximum Voltage        | Vmax       | Measurement on single-ended signal using absolute value. |     | 400 |     | 330 – 575              | mV    | 7,8     |

| Minimum Voltage        | Vmin       | (scope averaging off).                                   |     | 0   |     | -150 – 75              |       | 1,5,7,8 |

| Crossing Voltage (abs) | Vcross_abs | Scope averaging off.                                     |     | 200 |     | 125 – 275              | mV    | 1,6,7   |

| Crossing Voltage (var) | Δ-Vcross   | Scope averaging off.                                     |     | 0   |     | 70                     | mV    | 1,6,7   |

<sup>&</sup>lt;sup>1</sup> Guaranteed by design and characterization, not 100% tested in production.

#### **Table 13. Crystal Parameters**

TA = TAMB. Supply voltages per normal operation conditions; see Test Loads for loading conditions.

| Parameter                       | Symbol              | Conditions                               | MIN | TYP | MAX | Units | Notes |

|---------------------------------|---------------------|------------------------------------------|-----|-----|-----|-------|-------|

| Crystal Frequency               | F <sub>IN</sub>     |                                          |     | 25  |     | MHz   |       |

| Shunt Capacitance               | CO                  |                                          |     |     | 4   | pF    |       |

| Load Capacitance                | CL                  | Small range around CL only.              |     | 8   |     | pF    | 1     |

| Equivalent Series<br>Resistance | ESR                 | ESR defined at frequency of oscillation. |     |     | 50  | Ω     |       |

| Drive Level                     | DL                  | Drive Level to the crystal.              |     | 100 |     | μW    |       |

| Frequency Tolerance             | △F/ F <sub>IN</sub> | All operating temperature range.         |     |     | ±20 | PPM   | 2     |

<sup>&</sup>lt;sup>1</sup> When driven by an external oscillator via the XIN\_CLKIN pin, XOUT should be floating.

<sup>&</sup>lt;sup>2</sup> Measured from differential waveform.

<sup>&</sup>lt;sup>3</sup> Slew rate is measured through the Vswing voltage range centered around differential 0 V. This results in a ±75mV window around differential 0V

<sup>&</sup>lt;sup>4</sup> Matching applies to rising edge rate for Clock and falling edge rate for Clock#. It is measured using a ±37mV window centered on the average cross point where Clock rising meets Clock# falling. The median cross point is used to calculate the voltage thresholds the oscilloscope is to use for the edge rate calculations.

<sup>&</sup>lt;sup>5</sup> Vcross is defined as voltage where Clock = Clock# measured on a component test board and only applies to the differential rising edge (i.e. Clock rising and Clock# falling).

<sup>&</sup>lt;sup>6</sup> The total variation of all Vcross measurements in any particular system. Note that this is a subset of Vcross\_min/max (Vcross absolute) allowed. The intent is to limit Vcross induced modulation by setting Δ-Vcross to be smaller than Vcross absolute.

<sup>&</sup>lt;sup>7</sup> At default SMBus settings.

<sup>&</sup>lt;sup>8</sup> Includes 150mV of overshoot for Vmax and 150mV of undershoot for Vmin.

<sup>&</sup>lt;sup>2</sup> These parameters depend on specific customer requirements and may differ from the values listed here.

#### Table 14. PFT\_IN Clock Input Parameters

TA = TAMB. Supply voltages per normal operation conditions; see Test Loads for loading conditions.

| Parameter               | Symbol          | Conditions                                                 | MIN | TYP | MAX  | Units | Notes |

|-------------------------|-----------------|------------------------------------------------------------|-----|-----|------|-------|-------|

| Input Crossover Voltage | VCROSS          | Crossover voltage.                                         | 100 |     | 1000 | mV    |       |

| Input Swing             | VSWING          | Differential value.                                        | 200 |     | 2000 | mV    |       |

| Input Slew Rate         | dv/dt           | Measured differentially.                                   | 0.7 |     |      | V/ns  | 1     |

| Input Leakage Current   | I <sub>IN</sub> | V <sub>IN</sub> = 0.8V <sub>,</sub> V <sub>IN</sub> = GND. | -10 |     | 16   | μА    |       |

<sup>&</sup>lt;sup>1</sup> Slew rate measured through ±75mV window centered around differential zero.

#### **Table 15. Current Consumption**

TA = TAMB. Supply voltages per normal operation conditions; see Test Loads for loading conditions.

| Parameter                    | Symbol               | Conditions                                   | MIN | TYP | MAX | Units | Notes |

|------------------------------|----------------------|----------------------------------------------|-----|-----|-----|-------|-------|

|                              | IDDMXCK              | VDDMXCK, MXCK[2:1] at 100MHz.                |     | 30  |     | mA    | 1     |

|                              | I <sub>DD100M</sub>  | VDD100M, 100M[5:0].                          |     | 55  |     | mA    | 1     |

|                              | I <sub>DDXO</sub>    | VDDXO, 25MHz XTAL.                           |     | 25  |     | mA    | 1     |

| Operating                    |                      | 25M[2] on. PFT circuit active.               |     | 30  |     | mA    | 1     |

| Supply Current               | I <sub>DD</sub>      | 25M[2] on. PFT circuit not used (no PFT_IN). |     | 28  |     | mA    | 1     |

|                              | IDDA100M             | VDDA100M, 100M[5:0] at 100M,<br>SSC_EN =0    |     | 30  |     | mA    | 1     |

|                              | IDDMXCK              |                                              |     | 2.5 |     | mA    | 2     |

|                              | I <sub>DD100M</sub>  |                                              |     | 2.5 |     | mA    | 2     |

| Power Down<br>Supply Current | I <sub>DDXO</sub>    |                                              |     | 5   |     | mA    | 2     |

|                              | I <sub>DD</sub>      |                                              |     | 15  |     | mA    | 2     |

|                              | I <sub>DDA100M</sub> |                                              |     | 0.5 |     | mA    | 2     |

<sup>&</sup>lt;sup>1</sup> PWRGD = 1, all outputs enabled.

#### **Table 16. Power Supply Noise Profile**

TA = TAMB. Supply voltages per normal operation conditions; see Test Loads for loading conditions.

| Parameter Symbol      |                     | Conditions                                       | MIN | TYP | MAX | Units | Notes |

|-----------------------|---------------------|--------------------------------------------------|-----|-----|-----|-------|-------|

|                       | V <sub>DD_AC</sub>  | Single tone AC noise, swept.                     |     | 40  |     | mV    | 1     |

| Power Supply<br>Noise | V <sub>DDA_AC</sub> | V <sub>DD</sub> electrical noise > 20MHz.        |     | 20  |     | mV    | 1     |

| Noise                 | V <sub>DDXO</sub>   | V <sub>DD</sub> electrical noise 12kHz to 25MHz. |     | TBD |     | mV    | 1     |

14

$<sup>^{2}</sup>$  PWRGD = 0.

<sup>&</sup>lt;sup>1</sup> Peak-to-peak values. The device meets all AC/DC parameters in the presence of at least this much noise.

#### **Test Loads**

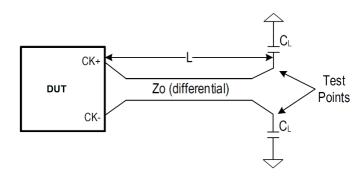

### Figure 10. AC/DC Test Load for Differential Outputs (Standard PCIe Source-Terminated)

Table 17. Parameters for AC/DC Test Load

| Rs(Ω)    | Zo(Ω) | L (cm) | C <sub>L</sub> (pF) |

|----------|-------|--------|---------------------|

| Internal | 85    | 25.4   | 2                   |

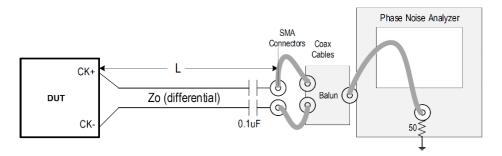

Figure 11. Test Load for PCle Phase Jitter Measurements

Table 18. Parameters for PCle Gen5 Jitter Measurement

| Rs(Ω)    | Ζο (Ω) | L (cm) * | C <sub>L</sub> (pF) |

|----------|--------|----------|---------------------|

| Internal | 85     | 25.4     | N/A                 |

<sup>\*</sup> Note: PCIe Gen5 specifies L = 0cm. L = 25.4cm is more conservative.

#### **SMBus Interface Information**

#### **Write Operation**

- Controller (host) sends a start bit

- Controller (host) sends the write address

- RSM clock will acknowledge

- Controller (host) sends the beginning byte location = N

- RSM clock will acknowledge

- Controller (host) sends the byte count = X

- RSM clock will acknowledge

- Controller (host) starts sending Byte N through Byte N+X-1

- RSM clock will acknowledge each byte one at a time

- Controller (host) sends a stop bit

|           | Write Operation |        |                      |  |  |  |  |  |  |

|-----------|-----------------|--------|----------------------|--|--|--|--|--|--|

| Controll  | er (Host)       |        | RSM (Slave/Receiver) |  |  |  |  |  |  |

| Т         | start bit       |        |                      |  |  |  |  |  |  |

| Slave     | Address         |        |                      |  |  |  |  |  |  |

| WR        | Write           |        |                      |  |  |  |  |  |  |

|           |                 |        | ACK                  |  |  |  |  |  |  |

| Beginnin  | g Byte = N      |        |                      |  |  |  |  |  |  |

|           |                 |        | ACK                  |  |  |  |  |  |  |

| Data Byte | e Count = X     |        |                      |  |  |  |  |  |  |

|           |                 |        | ACK                  |  |  |  |  |  |  |

| Beginni   | ng Byte N       |        |                      |  |  |  |  |  |  |

|           |                 |        | ACK                  |  |  |  |  |  |  |

| 0         |                 |        |                      |  |  |  |  |  |  |

| 0         |                 | X Byte | 0                    |  |  |  |  |  |  |

| 0         |                 | ਰ      | 0                    |  |  |  |  |  |  |

|           |                 |        | 0                    |  |  |  |  |  |  |

| Byte N    | Byte N + X - 1  |        |                      |  |  |  |  |  |  |

|           |                 |        | ACK                  |  |  |  |  |  |  |

| Р         | stop bit        |        |                      |  |  |  |  |  |  |

#### **Read Operation**

- Controller (host) will send a start bit

- Controller (host) sends the write address

- RSM clock will acknowledge

- Controller (host) sends the beginning byte location = N

- RSM clock will acknowledge

- Controller (host) will send a separate start bit

- Controller (host) sends the read address

- RSM clock will acknowledge

- RSM clock will send the data byte count = X

- RSM clock sends Byte N+X-1

- RSM clock sends Byte 0 through Byte X (if X(H) was written to Byte 8)

- Controller (host) will need to acknowledge each byte

- Controller (host) will send a not acknowledge bit

- Controller (host) will send a stop bit

|      | Read Operation  |        |                      |  |  |  |  |

|------|-----------------|--------|----------------------|--|--|--|--|

| Cor  | ntroller (Host) |        | RSM (Slave/Receiver) |  |  |  |  |

| Т    | start bit       |        |                      |  |  |  |  |

| SI   | ave Address     |        |                      |  |  |  |  |

| WR   | Write           |        |                      |  |  |  |  |

|      |                 |        | ACK                  |  |  |  |  |

| Begi | nning Byte = N  |        |                      |  |  |  |  |

|      |                 |        | ACK                  |  |  |  |  |

| RT   | Repeat start    |        |                      |  |  |  |  |

| SI   | ave Address     |        |                      |  |  |  |  |

| RD   | Read            |        |                      |  |  |  |  |

|      |                 |        | ACK                  |  |  |  |  |

|      |                 |        |                      |  |  |  |  |

|      | l               |        | Data Byte Count=X    |  |  |  |  |

|      | ACK             |        |                      |  |  |  |  |

|      |                 |        | Beginning Byte N     |  |  |  |  |

|      | ACK             |        |                      |  |  |  |  |

|      |                 | Φ      | 0                    |  |  |  |  |

|      | 0               | X Byte | 0                    |  |  |  |  |

|      | 0               |        | 0                    |  |  |  |  |

| 0    |                 |        |                      |  |  |  |  |

|      |                 |        | Byte N + X - 1       |  |  |  |  |

| N    | Not acknowledge |        |                      |  |  |  |  |

| Р    | stop bit        |        |                      |  |  |  |  |

**Table 19. SMBus Address Selection**

| SADR1 | SADR0 | SMBus Address |

|-------|-------|---------------|

| L     | L     | D2            |

| L     | М     | D4            |

| L     | Н     | D6            |

| M     | L     | B2            |

| М     | М     | B4            |

| M     | Н     | B6            |

| Н     | L     | ВА            |

| Н     | М     | ВС            |

| Н     | Н     | BE            |

Table 20. Byte 0: Output Enable Control Register

| Bit | Description                        | Bit = 0  | Bit = 1 | Туре | Default | Output(s) Affected |

|-----|------------------------------------|----------|---------|------|---------|--------------------|

| 7   | Reserved (Should be write to 1b'0) |          |         |      |         |                    |

| 6   | Reserved (Should be write to 1b'0) |          |         |      |         |                    |

| 5   | Output Enable 100M5                | Disabled | Enabled | RW   | 1       | 100M5              |

| 4   | Output Enable 100M4                | Disabled | Enabled | RW   | 1       | 100M4              |

| 3   | Output Enable 100M3                | Disabled | Enabled | RW   | 1       | 100M3              |

| 2   | Output Enable 100M2                | Disabled | Enabled | RW   | 1       | 100M2              |

| 1   | Output Enable 100M1                | Disabled | Enabled | RW   | 1       | 100M1              |

| 0   | Output Enable 100M0                | Disabled | Enabled | RW   | 1       | 100M0              |

Table 21. Byte 1: Output Enable Control Register

| Bit | Description                        | Bit = 0  | Bit = 1 | Туре | Default | Output(s) Affected |

|-----|------------------------------------|----------|---------|------|---------|--------------------|

| 7   | Reserved (Should be write to 1b'0) |          |         |      |         |                    |

| 6   | Reserved (Should be write to 1b'0) |          |         |      |         |                    |

| 5   | Output Enable MXCK2                | Disabled | Enabled | RW   | 1       | MXCK2              |

| 4   | Reserved (Should be write to 1b'0) |          |         |      |         |                    |

| 3   | Reserved (Should be write to 1b'0) |          |         |      |         |                    |

| 2   | Output Enable MXCK1                | Disabled | Enabled | RW   | 1       | MXCK1              |

| 1   | Reserved (Should be write to 1b'0) |          |         |      |         |                    |

| 0   | Reserved (Should be write to 1b'0) |          |         |      |         |                    |

17

#### Table 22. Byte 2: Output Enable Control Register

| Bit | Description          | Bit = 0  | Bit = 1          | Туре | Default | Output(s) Affected |

|-----|----------------------|----------|------------------|------|---------|--------------------|

| 7   | MXCK_SEL             | 100MHz   | 25MHz            | R/W  | 0       | MXCK [2:1]         |

| 6   | MXCK_SEL Control (1) | Reserved | Register control | R/W  | 0       | MXCK [2:1]         |

| 5   | Reserved             |          |                  |      |         |                    |

| 4   | Reserved             |          |                  |      |         |                    |

| 3   | Reserved             |          |                  |      |         |                    |

| 2   | Output Enable 25M2   | Disabled | Enabled          | RW   | 1       | 25M2               |

| 1   | Reserved             |          |                  |      |         |                    |

| 0   | Reserved             |          |                  |      |         |                    |

#### Note:

The MXCK\_SEL Control (bit 6) should be set to '1' then MXCK [2:1] outputs are controlled with MXCK\_SEL bit (bit 7).

#### Table 23. Byte 3: PFT Control Register

| Bit | Description                                    | Bit = 0       | Bit = 1             | Туре | Default  | Output(s) Affected |

|-----|------------------------------------------------|---------------|---------------------|------|----------|--------------------|

| 7   | Realtime Readback of PFT_LOST#                 | PFT_LOST# low | PFT_LOST# high      | R    | Realtime |                    |

| 6   | Stop Delta Frequency Update (Byte 4 and 5)     | Disabled      | Enabled             | R/W  | 0        | Reserved           |

| 5   | Clear Delta Frequency Registers (Byte 4 and 5) |               | All bits reset to 0 | RW   | 0        | Reserved           |

| 4   | Reserved                                       |               |                     |      | 0        | Reserved           |

| 3   | Reserved                                       |               |                     |      | 0        | Reserved           |

| 2   | Reserved                                       |               |                     |      | 0        | Reserved           |

| 1   | Reserved                                       |               |                     |      | 0        | Reserved           |

| 0   | Reserved                                       |               |                     |      | 0        | Reserved           |

#### Note:

Prior to reading the delta frequency between PFT\_IN and local 25MHz XO (Bytes 4 and 5), user should set bit 6 to prevent the case where one of the PFT Frequency Delta Registers is read before and the other after the internal update. The bit should be cleared after the read has been completed.

18

#### Table 24. Byte 4: PFT Frequency Delta Register 0 (Least Significant Byte)

| Bit | Description           | Bit = 0 | Bit = 1 | Туре | Default  | Output(s) Affected |

|-----|-----------------------|---------|---------|------|----------|--------------------|

| 7   | PFT – 25 MHz XO bit 7 |         |         | R    | Realtime |                    |

| 6   | PFT – 25 MHz XO bit 6 |         |         | R    | Realtime |                    |

| 5   | PFT – 25 MHz XO bit 5 |         |         | R    | Realtime |                    |

| 4   | PFT – 25MHz XO bit 4  |         |         | R    | Realtime |                    |

| 3   | PFT – 25 MHz XO bit 3 |         |         | R    | Realtime |                    |

| 2   | PFT – 25 MHz XO bit 2 |         |         | R    | Realtime |                    |

| 1   | PFT – 25 MHz XO bit 1 |         |         | R    | Realtime |                    |

| 0   | PFT – 25 MHz XO bit 0 |         |         | R    | Realtime |                    |

#### Note

These bits contain the least significant byte of average PPM difference between the PFT clock and the local 25MHz reference.

#### Table 25. Byte 5: PFT Frequency Delta Register 1 (Most Significant Byte)

| Bit | Description            | Bit = 0         | Bit = 1         | Туре | Default  | Output(s) Affected |

|-----|------------------------|-----------------|-----------------|------|----------|--------------------|

| 7   | PFT – Sign Bit         | Positive Number | Negative Number | R    | Realtime |                    |

| 6   | PFT – 25 MHz XO bit 14 |                 |                 | R    | Realtime |                    |

| 5   | PFT – 25 MHz XO bit 13 |                 |                 | R    | Realtime |                    |

| 4   | PFT – 25 MHz XO bit 12 |                 |                 | R    | Realtime |                    |

| 3   | PFT – 25 MHz XO bit 11 |                 |                 | R    | Realtime |                    |

| 2   | PFT – 25 MHz XO bit 10 |                 |                 | R    | Realtime |                    |

| 1   | PFT – 25 MHz XO bit 9  |                 |                 | R    | Realtime |                    |

| 0   | PFT – 25 MHz XO bit 8  |                 |                 | R    | Realtime |                    |

#### Note:

These bits contain the most significant byte of average PPM difference between the PFT clock and the local 25MHz reference. The representation is 2's complement, signed magnitude with Byte 5 bit 7 being the sign bit.

19

### Table 26. Byte 6: SSC PLL Control Register

| Bit | Description            | Bit = 0                             | Bit = 1             | Туре | Default                   | Output(s) Affected                 |

|-----|------------------------|-------------------------------------|---------------------|------|---------------------------|------------------------------------|

| 7   | Reserved               |                                     |                     |      | Reserved                  | Reserved                           |

| 6   | Reserved               |                                     |                     |      | Reserved                  | Reserved                           |

| 5   |                        | Bit [1:0]: S                        | SC State            | R    | Realtime                  |                                    |

| 4   | Readback of SSC_EN pin | 00: SSC Off, 01<br>10: Reserved, 11 |                     | R    | Realtime                  |                                    |

| 3   | SSC PLL Input Source   | XTAL                                | Filter PLL          | RW   | 0                         | 100M[5:0]                          |

| 2   | SSC Pin Control        | Pin Control                         | Software<br>Control | RW   | 0                         | and<br>MXCK[2:1] if<br>MXCK SEL= 0 |

| 1   | SSC Select             | Bit [1:0]: S                        |                     | RW   | Latch SSC pin on power-up | WINON_SEL= 0                       |

| 0   | SSC Select             | 00: SSC Off, 01<br>10: Reserved, 11 |                     | RW   | Latch SSC pin on power-up |                                    |

### Byte 7: Reserved

### Table 27. Byte 8: Vendor/Revision Identification Control Register

| Bit | Description         | Bit = 0                         | Bit = 1 | Туре | Default | Output(s) Affected |

|-----|---------------------|---------------------------------|---------|------|---------|--------------------|

| 7   | Revision Code Bit 3 |                                 |         | R    | 0       |                    |

| 6   | Revision Code Bit 2 |                                 |         | R    | 0       |                    |

| 5   | Revision Code Bit 1 | 0000 is 1 <sup>St</sup> Silicon |         | R    | 0       |                    |

| 4   | Revision Code Bit 0 |                                 |         | R    | 0       |                    |

| 3   | Vendor ID Bit 3     |                                 |         | R    | 0       |                    |

| 2   | Vendor ID Bit 2     | 0004 in DCM                     |         | R    | 0       |                    |

| 1   | Vendor ID Bit 1     | 0001 is RSM                     |         | R    | 0       |                    |

| 0   | Vendor ID Bit 0     |                                 |         | R    | 1       |                    |

### Table 28. Byte 9: Device ID Control Register

| Bit | Description       | Bit = 0           | Bit = 1 | Туре | Default | Output(s) Affected |

|-----|-------------------|-------------------|---------|------|---------|--------------------|

| 7   | Device ID 7 (MSB) |                   | R       | 0    |         |                    |

| 6   | Device ID 6       | RS2CG2008 is 0h40 |         | R    | 1       |                    |

| 5   | Device ID 5       |                   |         | R    | 0       |                    |

| 4   | Device ID 4       |                   |         | R    | 0       |                    |

| 3   | Device ID 3       |                   |         | R    | 0       |                    |

| 2   | Device ID 2       |                   |         | R    | 0       |                    |

| 1   | Device ID 1       |                   |         | R    | 0       |                    |

| 0   | Device ID 0       |                   |         | R    | 0       |                    |

## Table 29. Byte 10: Byte Count Register

| Bit | Description                                                                | Bit = 0 | Bit = 1 | Туре | Default | Output(s) Affected |

|-----|----------------------------------------------------------------------------|---------|---------|------|---------|--------------------|

| 7   | Reserved                                                                   |         |         |      | 0       |                    |

| 6   | Reserved                                                                   |         |         |      | 0       |                    |

| 5   | BC5 - Writing to this register configures how many bytes will be read back |         |         | RW   | 0       |                    |

| 4   | BC4 - Writing to this register configures how many bytes will be read back |         |         | RW   | 0       |                    |

| 3   | BC3 - Writing to this register configures how many bytes will be read back |         |         | RW   | 1       |                    |

| 2   | BC2 - Writing to this register configures how many bytes will be read back |         |         | RW   | 0       |                    |

| 1   | BC1 - Writing to this register configures how many bytes will be read back |         |         | RW   | 0       |                    |

| 0   | BC0 - Writing to this register configures how many bytes will be read back |         |         | RW   | 0       |                    |

21

Byte 11~Byte16: Reserved

## **Package Information**

#### TQFN\_48L

# **Revision History**

| Revision | Description     | Date       |

|----------|-----------------|------------|

| 1.0      | Initial release | 2024/11/28 |

|          |                 |            |