## **Features**

- No Direction-Control

- Max Data Rates

24Mbps (Push-Pull)

2Mbps (Open-Drain)

- 1.2V to 3.63V on A ports and 1.2V to 3.63V on B Ports

- VCCA can be Less than, Greater than or Equal to VCCB

- VCC Isolation: If Either VCC is at GND, Both Ports are in the High-Impedance State

- No Power-Supply Sequencing Required: VCCA or VCCB can be Ramped First

- ESD protection exceeds 6000V HBM, 1000V CDM

- AEC-Q100 qualified, PPAP capable, and manufactured in IATF 16949 certified facilities.

- Grade 1 temperature range (- 40°C ~ +125 °C)

## **Applications**

- I2C/SMBus

- SPI Interface

- UART

- Handheld Devices Interface

## **Description**

The RS7LS104Q is a 4-bit configurable dual supply bidirectional auto sensing translator that does not require a directional control pin. The A and B ports are designed to track two different power supply rails, VCCA and VCCB respectively.

A port supporting operating voltages from 1.2V to 3.63V while it tracks the VCCA supply, and the B ports supporting operating voltages from 1.2V to 3.63V while it tracks the VCCB supply. This allows the support of both lower and higher logic signal levels while providing bidirectional translation capabilities between any of the 1.2V,1.8V, 2.5V, 3.3V voltage and 3.63V nodes.

When the output-enable (EN) input is low, all outputs are placed in the high-impedance state. To ensure the high-impedance state during power up or power down, EN should be tied to GND through a pulldown resistor; the minimum value of the resistor is determined by the current-sourcing capability of the driver.

# **Ordering Information**

| Ordering Code | Package | Description            |

|---------------|---------|------------------------|

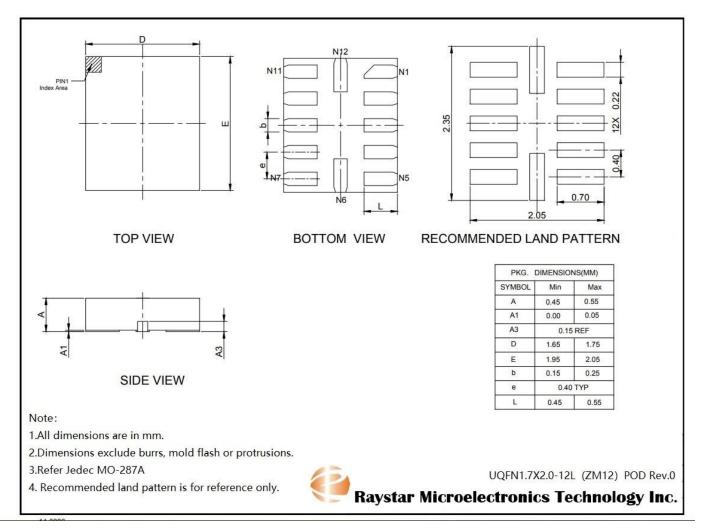

| RS7LS104QZME  | ZM      | UQFN-12, 1.7mmx2.0 mm  |

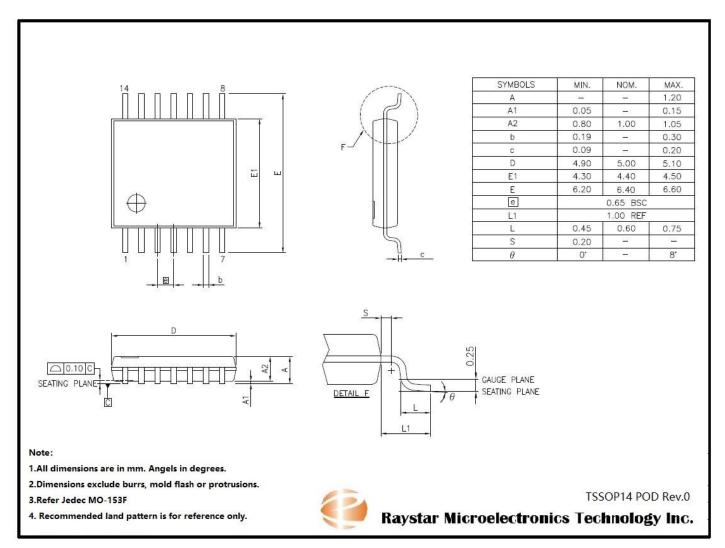

| RS7LS104QLE   | L       | TSSOP-14, pitch 0.65mm |

| RS7LS104QZBE  | ZB      | TQFN-14, 3.5mmX3.5mm   |

Notes:

E = Pb-free and Green

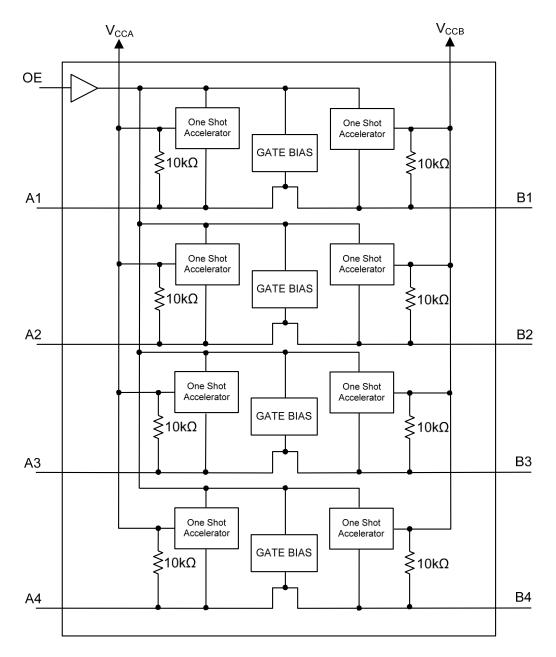

# **Block Diagram**

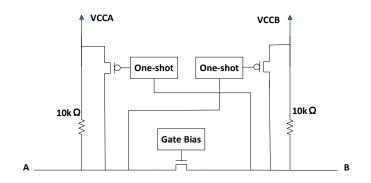

Figure 1 Block Diagram

# **Pin Configuration**

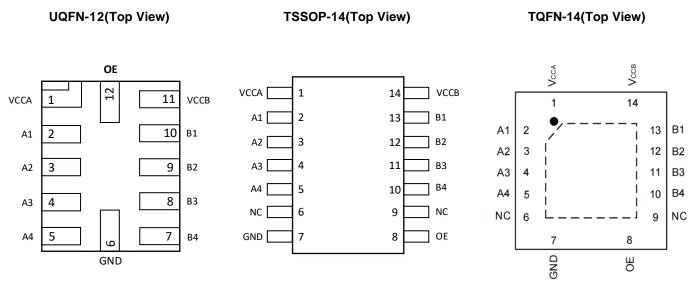

### Figure 2 Pin Configuration

| Pin Name | UQFN-12 | TSSOP-14 | TQFN-14 | Description                                                                        |

|----------|---------|----------|---------|------------------------------------------------------------------------------------|

| VCCA     | 1       | 1        | 1       | A-port supply voltage.1.2V ≤ VCCA ≤3.63 V                                          |

| A1       | 2       | 2        | 2       | Input/output A. Referenced to VCCA.                                                |

| A2       | 3       | 3        | 3       | Input/output A. Referenced to VCCA                                                 |

| A3       | 4       | 4        | 4       | Input/output A. Referenced to VCCA                                                 |

| A4       | 5       | 5        | 5       | Input/output A. Referenced to VCCA                                                 |

| GND      | 6       | 7        | 7       | Ground.                                                                            |

| OE       | 12      | 8        | 8       | Output enables (active High).<br>Pull OE low to place all outputs in 3-state mode. |

| B4       | 7       | 10       | 10      | Input/output B. Referenced to VCCB                                                 |

| B3       | 8       | 11       | 11      | Input/output B. Referenced to VCCB                                                 |

| B2       | 9       | 12       | 12      | Input/output B. Referenced to VCCB                                                 |

| B1       | 10      | 13       | 13      | Input/output B. Referenced to VCCB                                                 |

| VCCB     | 11      | 14       | 14      | B-port supply voltage.1.2V ≤ VCCB ≤3.63V                                           |

| NC       | /       | 6,9      | 6,9     | Not Connect                                                                        |

## **Absolute Maximum Ratings**

| Symbol | Parameter                                  | MIN  | ТҮР | MAX | Unit |

|--------|--------------------------------------------|------|-----|-----|------|

| Tstore | Storage Temperature                        | -65  | -   | 150 | °C   |

| VCCA   | DC Supply Voltage port B                   | -0.3 | -   | 5.5 | V    |

| VCCB   | DC Supply Voltage port A                   | -0.3 | -   | 5.5 | V    |

| VIOB   | Vi(A) referenced DC Input / Output Voltage | -0.3 | -   | 5.5 | V    |

| VIOB   | Vi(B) referenced DC Input / Output Voltage | -0.3 | -   | 5.5 | V    |

| VEN    | Enable Control Pin DC Input Voltage        | -0.3 | -   | 5.5 | V    |

| Ishort | Short circuit duration (I/O to GND)        |      |     | 50  | mA   |

#### Notes:

Stresses greater than those listed under MAXIMUM RATINGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

## **Recommended operation conditions**

| Symbol | Parameter                          | MIN | TYP | MAX  | Unit |

|--------|------------------------------------|-----|-----|------|------|

| VCCA   | VCCA Positive DC Supply Voltage    | 1.2 | -   | 3.63 | V    |

| VCCB   | VCCB Positive DC Supply Voltage    | 1.2 | -   | 3.63 | V    |

| VEN    | Enable Control Pin Voltage         | GND | -   | 3.63 | V    |

| VIO    | I/O Pin Voltage                    | GND | -   | 3.63 | V    |

| Δt /ΔV | Input transition rise or fall time | -   | -   | 10   | ns/V |

| ТА     | Operating Temperature Range        | -40 | -   | 125  | °C   |

## **DC Electrical Characteristics**

Unless otherwise specified, -40°C≤T\_a≤125° C,  $1.2V{\le}V{\tiny\tt CCA}{\le}3.63V$  ,  $1.2V{\le}V{\tiny\tt CCB}{\le}3.63V$

| Symbol        | Parameter                      | Test Conditions*1 |                                           | MIN        | TYP | MAX        | Unit |

|---------------|--------------------------------|-------------------|-------------------------------------------|------------|-----|------------|------|

|               |                                | 2.3V≤VCCA         | A ≤3.63V                                  | VCCA - 0.4 |     |            | V    |

| VIHA          | A port Input HIGH Voltage      | 1.2V≤VCCA < 2.3V  |                                           | VCCA - 0.2 |     |            | V    |

| VILA          | A port Input LOW Voltage       | 1.2V≤VCCA         | A ≤3.63V                                  | -          | -   | 0.15       | V    |

| VIHB          | B port Input HIGH Voltage      | 2.3V≤VCCE         | 3 ≤3.63V                                  | VCCB - 0.4 | -   | -          | V    |

| VIND          | B poit input high voitage      | 1.2V≤VCCA         | A <2.3V                                   | VCCB - 0.2 |     |            |      |

| VILB          | B port Input LOW Voltage       | 1.2V≤VCCE         | 3 ≤3.63V                                  | -          | -   | 0.15       | V    |

| VIH(EN)       | Control Pin Input HIGH Voltage | 1.2V≤VCCA         | A ≤3.63V                                  | 0.65*VCCA  | -   | -          | V    |

|               | Control Pin Input LOW Voltage  | 1.65V≤VCC         | CA ≤3.63V                                 | -          | -   | 0.35* VCCA |      |

| VIL(EN)       | Control Pill input LOW Voltage | 1.2V≤VCCA         | A < 1.65V                                 |            |     | 0.15       | V    |

| VOHA          | A port Output HIGH Voltage     | A port source     | ce current= -20 μA                        | 0.8* VCCA  | -   | -          | V    |

| VOLA          | A port Output LOW Voltage      | A port sink of    | current =1 mA                             | -          | -   | 0.4        | V    |

| VOHB          | B port Output HIGH Voltage     | B port source     | ce current = -20 μA                       | 0.8*VCCB   | -   | -          | V    |

| VOLB          | B port Output LOW Voltage      | B port sink of    | current =1 mA                             | -          | -   | 0.4        | V    |

|               |                                |                   | VCCA=1.2V to 3.63V,<br>VCCB=1.2V to 3.63V | -          | 0.2 | 2.4        | μA   |

| ICCA          | VCCA Supply Current            | OE=High           | VCCA= 3.63V, VCCB= 0V                     | -          | -   | 2          | μA   |

|               |                                |                   | VCCA= 0V, VCCB=3.63V                      | -          | -   | 1          | μA   |

|               |                                |                   | VCCA=1.2V to 3.63V,<br>VCCB=1.2V to 3.63V | -          | 0.5 | 10         | μA   |

| ICCB          | VCCB Supply Current            | OE=High           | VCCA= 3.63V, VCCB= 0V                     | -          |     | 1          | μA   |

|               |                                |                   | VCCA= 0V, VCCB=3.63V                      | -          |     | 8          | μA   |

| ICCA<br>+ICCB | Combined supply current        | OE=High           | VCCA=1.2V to 3.63V,<br>VCCB=1.2V to 3.63V |            |     | 15         | μA   |

| ICCZA         | Static supply current VCCA     | 05.1.00           | VCCA=1.2V to 3.63V,                       |            |     | 8          | μA   |

| ICCZB         | Static supply current VCCB     | OE=Low            | VCCB=1.2V to 3.63V                        |            |     | 8          | μA   |

| IOZ           | I/O Tri-state Output Mode      | A or B            | VIA=0~VCCA                                |            |     | . 0        |      |

| 102           | Leakage Current                | Port              | VIB=0~VCCB                                |            |     | ±8         | μA   |

|               |                                | A port            | A port VCCA=0V, VCCB=1.2V to 3.63V        |            |     | ±8         | μA   |

| IOFF          | Partial power down current     | B port            | VCCA=1.2V to 3.63V<br>VCCB=0V             |            |     | ±8         | μA   |

| II-EN         | Control pin leakage Current    | VI = VCCI or GND  |                                           | -          | -   | ±2         | μA   |

| RPU           | Pull-Up Resistors I/O A and B  | -                 | -                                         |            | 10  | -          | kΩ   |

| Ci            | EN                             | VCCA= 3.3         | V, VCCB= 3.3V                             | -          | -   | 1          | pF   |

| 00            | A port                         | VCCA= 3.3         | V, VCCB= 3.3V                             | -          | -   | 5          | pF   |

| CIO           | B port                         | VCCA= 3.3         | V, VCCB= 3.3V                             | -          | -   | 5          | pF   |

#### Note:

1. All units are production tested at TA =  $+25^{\circ}$ C. Limits over the operating temperature range are guaranteed by design. Typical values are for VCCB = +3.3 V, VCCA = +1.8 V and TA =  $+25^{\circ}$ C.

## **AC Electrical characteristics**

$C_{LOAD} = 15 pF$ , driver output impedance  $\leq 50 \Omega$ ,  $R_{LOAD} = 1 M\Omega$ , TA = -40°C to 125°C,

### V<sub>CCA</sub>= 1.2V

|                     | <b>P</b>                            | T               | VCCE | 3=1.8V | VCC | B=2.5V | VCCB | =3.3V |      |

|---------------------|-------------------------------------|-----------------|------|--------|-----|--------|------|-------|------|

| Symbol              | Parameter                           | Test Conditions | MIN  | MAX    | MIN | MAX    | MIN  | MAX   | Unit |

| +                   |                                     | Push-pull       |      | 12     |     | 10     |      | 10    | ns   |

| t <sub>PHL_AB</sub> | Propagation Delay A $\rightarrow$ B | Open-drain      |      | 30     |     | 30     |      | 30    | ns   |

| <b>+</b>            |                                     | Push-pull       |      | 20     |     | 15     |      | 15    | ns   |

| t <sub>PLH_AB</sub> | Propagation Delay A $\rightarrow$ B | Open-drain      |      | 30     |     | 30     |      | 30    | ns   |

| 4                   |                                     | Push-pull       |      | 12     |     | 10     |      | 10    | ns   |

| t <sub>PHL_BA</sub> | Propagation Delay $B \rightarrow A$ | Open-drain      |      | 30     |     | 30     |      | 30    | ns   |

| +                   |                                     | Push-pull       |      | 20     |     | 15     |      | 15    | ns   |

| t <sub>PLH_BA</sub> | Propagation Delay $B \rightarrow A$ | Open-drain      |      | 50     |     | 50     |      | 50    | ns   |

| t <sub>EN</sub>     | Enable Time                         | EN to A or B    |      | 380    |     | 200    |      | 200   | ns   |

| t <sub>DIS</sub>    | Disable Time                        | EN to A or B    |      | 200    |     | 200    |      | 200   | ns   |

| +                   | A nort Dine Time                    | Push-pull       |      | 30     |     | 30     |      | 30    | ns   |

| t <sub>RA</sub>     | A port Rise Time                    | Open-drain      |      | 160    |     | 120    |      | 120   | ns   |

|                     | Disast Disas Times                  | Push-pull       |      | 30     |     | 30     |      | 30    | ns   |

| t <sub>RB</sub>     | B port Rise Time                    | Open-drain      |      | 160    |     | 160    |      | 160   | ns   |

|                     |                                     | Push-pull       |      | 20     |     | 20     |      | 25    | ns   |

| t <sub>FA</sub>     | A port Fall Time                    | Open-drain      |      | 30     |     | 30     |      | 30    | ns   |

|                     |                                     | Push-pull       |      | 20     |     | 20     |      | 25    | ns   |

| t <sub>FB</sub>     | B port Fall Time                    | Open-drain      |      | 30     |     | 30     |      | 30    | ns   |

| t <sub>SKEW</sub>   | Channel to Channel                  | el Skew         |      | 1      |     | 1      |      | 1     | ns   |

|                     |                                     | Push-pull       | 20   |        | 20  |        | 20   |       | Mbps |

| MDR                 | Maximum Data Rate                   | Open-drain      | 2    |        | 2   |        | 2    |       | Mbps |

### VCCA= 1.8V

| Symbol              | Parameter                           | Test Conditions | VCC | B=1.2V | VCC | B=2.5V | VCCB | = 3.3V |      |

|---------------------|-------------------------------------|-----------------|-----|--------|-----|--------|------|--------|------|

| Symbol              | Parameter                           | Test Conditions | MIN | MAX    | MIN | MAX    | MIN  | MAX    | Unit |

| +                   |                                     | Push-pull       |     | 12     |     | 10     |      | 9      | ns   |

| t <sub>PHL_AB</sub> | Propagation Delay A $\rightarrow$ B | Open-drain      |     | 30     |     | 30     |      | 30     | ns   |

|                     |                                     | Push-pull       |     | 20     |     | 12     |      | 11     | ns   |

| t <sub>PLH_AB</sub> | Propagation Delay A $\rightarrow$ B | Open-drain      |     | 30     |     | 30     |      | 30     | ns   |

|                     |                                     | Push-pull       |     | 12     |     | 9      |      | 9      | ns   |

| t <sub>PHL_BA</sub> | Propagation Delay $B \rightarrow A$ | Open-drain      |     | 30     |     | 30     |      | 30     | ns   |

|                     |                                     | Push-pull       |     | 20     |     | 14     |      | 12     | ns   |

| t <sub>PLH_BA</sub> | Propagation Delay B →A              | Open-drain      |     | 50     |     | 50     |      | 50     | ns   |

| t <sub>EN</sub>     | Enable Time                         | EN to A or B    |     | 200    |     | 200    |      | 200    | ns   |

| t <sub>DIS</sub>    | Disable Time                        | EN to A or B    |     | 200    |     | 200    |      | 200    | ns   |

|                     | A next Dies Time                    | Push-pull       |     | 30     |     | 30     |      | 30     | ns   |

| t <sub>RA</sub>     | A port Rise Time                    | Open-drain      |     | 160    |     | 120    |      | 120    | ns   |

|                     | B port Rise Time                    | Push-pull       |     | 30     |     | 30     |      | 30     | ns   |

| t <sub>RB</sub>     | B port Rise Time                    | Open-drain      |     | 160    |     | 160    |      | 160    | ns   |

|                     | A port Foll Time                    | Push-pull       |     | 20     |     | 20     |      | 25     | ns   |

| t <sub>FA</sub>     | A port Fall Time                    | Open-drain      |     | 30     |     | 30     |      | 30     | ns   |

|                     |                                     | Push-pull       |     | 20     |     | 25     |      | 30     | ns   |

| t <sub>FB</sub>     | B port Fall Time                    | Open-drain      |     | 30     |     | 30     |      | 30     | ns   |

| t <sub>SKEW</sub>   | Channel to Cha                      | annel Skew      |     | 1      |     | 1      |      | 1      | ns   |

|                     | Maximum Data D i                    | Push-pull       | 20  | 1      | 20  |        | 24   |        | Mbps |

| MDR                 | Maximum Data Rate                   | Open-drain      | 2   | 1      | 2   |        | 2    |        | Mbps |

## $V_{CCA}$ = 2.5V

| Symbol              | Parameter                           | Test Conditions | VCCE | B= 1.2V | VCCB | 8= 1.8V | VCCB | = 3.3V | Unit |

|---------------------|-------------------------------------|-----------------|------|---------|------|---------|------|--------|------|

| Cymbol              | rarameter                           |                 | MIN  | MAX     | MIN  | MAX     | MIN  | MAX    | onne |

| +                   |                                     | Push-pull       |      | 10      |      | 9       |      | 9      | ns   |

| t <sub>PHL_AB</sub> | Propagation Delay A $\rightarrow$ B | Open-drain      |      | 30      |      | 30      |      | 30     | ns   |

|                     |                                     | Push-pull       |      | 15      |      | 12      |      | 10     | ns   |

| t <sub>PLH_AB</sub> | Propagation Delay A $\rightarrow$ B | Open-drain      |      | 30      |      | 30      |      | 30     | ns   |

|                     |                                     | Push-pull       |      | 10      |      | 10      |      | 9      | ns   |

| t <sub>PHL_BA</sub> | Propagation Delay $B \rightarrow A$ | Open-drain      |      | 30      |      | 30      |      | 30     | ns   |

|                     |                                     | Push-pull       |      | 15      |      | 12      |      | 12     | ns   |

| t <sub>PLH_BA</sub> | Propagation Delay $B \rightarrow A$ | Open-drain      |      | 50      |      | 50      |      | 50     | ns   |

| t <sub>EN</sub>     | Enable Time                         | EN to A or B    |      | 200     |      | 200     |      | 200    | ns   |

| t <sub>DIS</sub>    | Disable Time                        | EN to A or B    |      | 200     |      | 200     |      | 200    | ns   |

|                     | A port Rise Time                    | Push-pull       |      | 30      |      | 30      |      | 30     | ns   |

| t <sub>RA</sub>     | A port Rise fille                   | Open-drain      |      | 160     |      | 120     |      | 120    | ns   |

|                     | D port Dice Time                    | Push-pull       |      | 30      |      | 30      |      | 30     | ns   |

| t <sub>RB</sub>     | B port Rise Time                    | Open-drain      |      | 160     |      | 160     |      | 160    | ns   |

|                     | A port Fall Time                    | Push-pull       |      | 20      |      | 25      |      | 30     | ns   |

| t <sub>FA</sub>     | A port Fail Time                    | Open-drain      |      | 30      |      | 30      |      | 30     | ns   |

|                     | D port Foll Time                    | Push-pull       |      | 20      |      | 20      |      | 25     | ns   |

| t <sub>FB</sub>     | B port Fall Time                    | Open-drain      |      | 30      |      | 30      |      | 30     | ns   |

| t <sub>SKEW</sub>   | Channel to Chan                     | nel Skew        |      | 1       |      | 1       |      | 1      | ns   |

| MDD                 | Maximum Data Rate                   | Push-pull       | 20   |         | 20   |         | 24   |        | Mbps |

| MDR                 | INIAXIMUM DAIA RALE                 | Open-drain      | 2    |         | 2    |         | 2    |        | Mbps |

## $V_{CCA}$ = 3.3V

| Cumhal              | Devementer                          | Toot Conditions | VCC | CB= 1.2V | VCC | B= 1.8V | VCC | B = 2.5V |      |

|---------------------|-------------------------------------|-----------------|-----|----------|-----|---------|-----|----------|------|

| Symbol              | Parameter                           | Test Conditions | MIN | MAX      | MIN | MAX     | MIN | MAX      | Unit |

| +                   |                                     | Push-pull       |     | 10       |     | 9       |     | 9        | ns   |

| t <sub>PHL_AB</sub> | Propagation Delay A $\rightarrow$ B | Open-drain      |     | 30       |     | 30      |     | 30       | ns   |

| 4                   |                                     | Push-pull       |     | 15       |     | 12      |     | 12       | ns   |

| t <sub>PLH_AB</sub> | Propagation Delay A $\rightarrow$ B | Open-drain      |     | 30       |     | 30      |     | 30       | ns   |

|                     |                                     | Push-pull       |     | 10       |     | 9       |     | 9        | ns   |

| t <sub>PHL_BA</sub> | Propagation Delay $B \rightarrow A$ | Open-drain      |     | 30       |     | 30      |     | 30       | ns   |

|                     |                                     | Push-pull       |     | 15       |     | 11      |     | 10       | ns   |

| t <sub>PLH_BA</sub> | Propagation Delay B →A              | Open-drain      |     | 50       |     | 50      |     | 50       | ns   |

| t <sub>EN</sub>     | Enable Time                         | EN to A or B    |     | 200      |     | 200     |     | 200      | ns   |

| t <sub>DIS</sub>    | Disable Time                        | EN to A or B    |     | 200      |     | 200     |     | 200      | ns   |

|                     | A port Disc Time                    | Push-pull       |     | 30       |     | 30      |     | 30       | ns   |

| t <sub>RA</sub>     | A port Rise Time                    | Open-drain      |     | 160      |     | 120     |     | 120      | ns   |

|                     | P port Pice Time                    | Push-pull       |     | 30       |     | 30      |     | 30       | ns   |

| t <sub>RB</sub>     | B port Rise Time                    | Open-drain      |     | 160      |     | 160     |     | 160      | ns   |

| 4                   | A port Fall Time                    | Push-pull       |     | 25       |     | 25      |     | 25       | ns   |

| t <sub>FA</sub>     | A port Fail Time                    | Open-drain      |     | 30       |     | 30      |     | 30       | ns   |

|                     | D port Foll Time                    | Push-pull       |     | 25       |     | 25      |     | 25       | ns   |

| t <sub>FB</sub>     | B port Fall Time                    | Open-drain      |     | 30       |     | 30      |     | 30       | ns   |

| t <sub>SKEW</sub>   | Channel to Channel Sk               | ew              |     | 1        |     | 1       |     | 1        | ns   |

| MDD                 | Maximum Data Data                   | Push-pull       | 20  | 1        | 24  |         | 24  |          | Mbps |

| MDR                 | Maximum Data Rate                   | Open-drain      | 2   | 1        | 2   |         | 2   |          | Mbps |

## Parameter Measurement Information

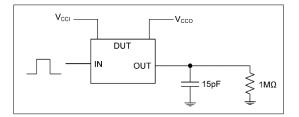

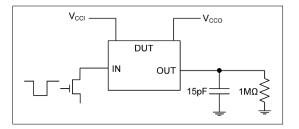

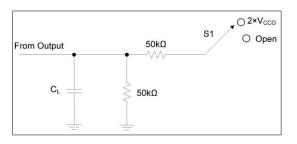

### **Load Circuits**

#### Figure 3 Data Rate, Pulse Duration, Propagation Delay, Output Rise-Time and Fall-Time Measurement Using a Push-Pull Driver

Figure 4 Data Rate, Pulse Duration, Propagation Delay, Output Rise-Time and Fall-Time Measurement Using an Open-Drain Driver

| TEST        | S1       |

|-------------|----------|

| tPZL / tPLZ | 2 × VCCO |

| tPHZ / Tpzh | Open     |

#### Figure 5 Load Circuit for Enable-Time and Disable-Time Measurement

#### Notes:

- 1. CL includes probe and jig capacitance.

- 2. ten is the same as tPZL and tPZH. tdis is the same as tPLZ and tPHZ.

- 3. VCCI is the supply voltage associated with the input.

- 4. VCCO is the supply voltage associated with the input.

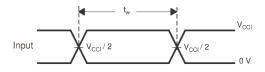

### **Voltage Waveforms**

The outputs are measured one at a time, with one transition per measurement. All input pulses are supplied by generators that have the following characteristics:

- PRR ≤10 MHz

- Z<sub>O</sub> = 50 Ω

- dv/dt ≥1 V/ns

**Figure 6 Pulse Duration**

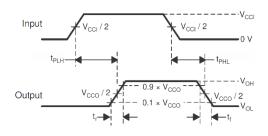

Figure 7 Propagation Delay Times

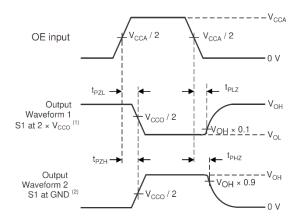

A. Waveform 1 is for an output with internal such that the output is high, except when OE is high.B. Waveform 2 is for an output with conditions such that the output is low, except when OE is high.

### Figure 8 Enable and Disable Times

## **Functional Description**

### Architecture

The RS7LS104Q architecture does not require a direction-control signal in order to control the direction of data flow from A to B or from B to A.

### Figure 9 Level Shifter Architecture

Each A-port I/O has an internal  $10k\Omega$  pull up resistor to  $V_{CCA}$ , and each B-port I/O has an internal  $10k\Omega$  pullup resistor to  $V_{CCB}$ . The output one-shots detect rising edges on the A or B ports. During a rising edge, the one-shot turns on the PMOS transistors for a short duration, which speeds up the low-to-high transition.

### Input Driver Requirements

The rise (tR) and fall (tF) timing parameters of the open drain outputs depend on the magnitude of the pull-up resistors. In -addition, the propagation times (tPD), skew (tSKEW) and maximum data rate depend on the impedance of the device that is connected to the translator. The timing parameters listed in the data sheet assume that the output impedance of the drivers connected to the translator is less than 50 k $\Omega$ .

### Enable Input (OE)

The RS7LS104Q has an Enable pin (OE) that provides tri-state operation at the I/O pins. Driving the Enable pin to a low logic level minimizes the power consumption of the device and drives the I/O VCCB and I/O VCCA pins to a high impedance state. Normal translation operation occurs when the OE pin is equal to a logic high signal. The OE pin is referenced to the VCCA supply and has overvoltage tolerant protection.

#### Pull-up or Pull-down Resistors on I/O Lines

Each A-port I/O has an internal  $10k\Omega$  pull-up resistor to VCCA, and each B-port I/O has an internal  $10 k\Omega$  pull-up resistor to VCCB. If a smaller value of pull-up resistor is required, an external resistor must be added from the I/O to VCCA or VCCB (in parallel with the internal  $10 k\Omega$  resistors).

#### **Device Functional Modes**

The RS7LS104Q device has two functional modes, enabled and disabled. To disable the device set the OE input low, which places all I/Os in a high impedance state. Setting the OE input high will enable the device.

## **Application Information**

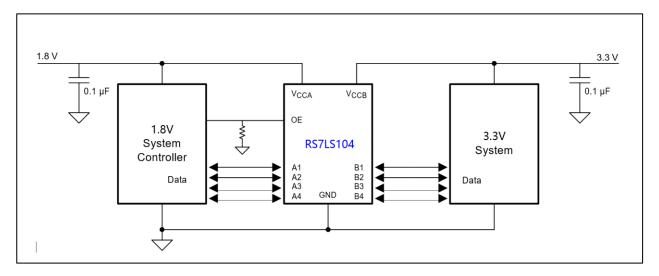

### Figure 10 Application Circuit

## Power Supply Guidelines

During normal operation, supply voltage V<sub>CCA</sub> can be greater than, less than or equal to V<sub>CCB</sub>. The sequencing of the power supplies will not damage the device during the power up operation. For optimal performance,  $0.01\mu$ F to  $0.1\mu$ F decoupling capacitors should be used on the V<sub>CCA</sub> and V<sub>CCB</sub> power supply pins. Ceramic capacitors are a good design choice to filter and bypass any noise signals on the voltage lines to the ground plane of the PCB. The noise immunity will be maximized by placing the capacitors as close as possible to the supply and ground pins, along with minimizing the PCB connection traces.

## **Package Information**

## UQFN 1.7x2.0-12L

### **TSSOP-14L**

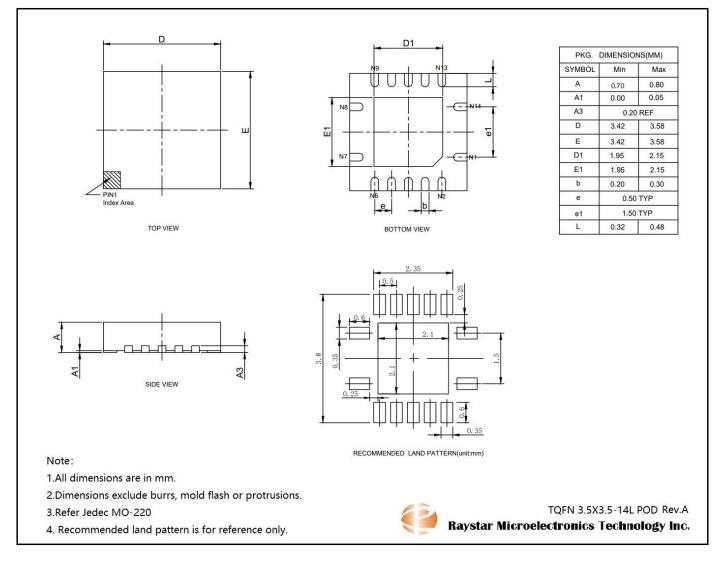

### TQFN3.5X3.5-14L

# **Revision History**

| Revision | Description                                  | DATE      |

|----------|----------------------------------------------|-----------|

| 1.0      | Initial Release                              | 2024/5/28 |

| 1.1      | ADD TQFN-14 package and ordering information | 2024/9/14 |